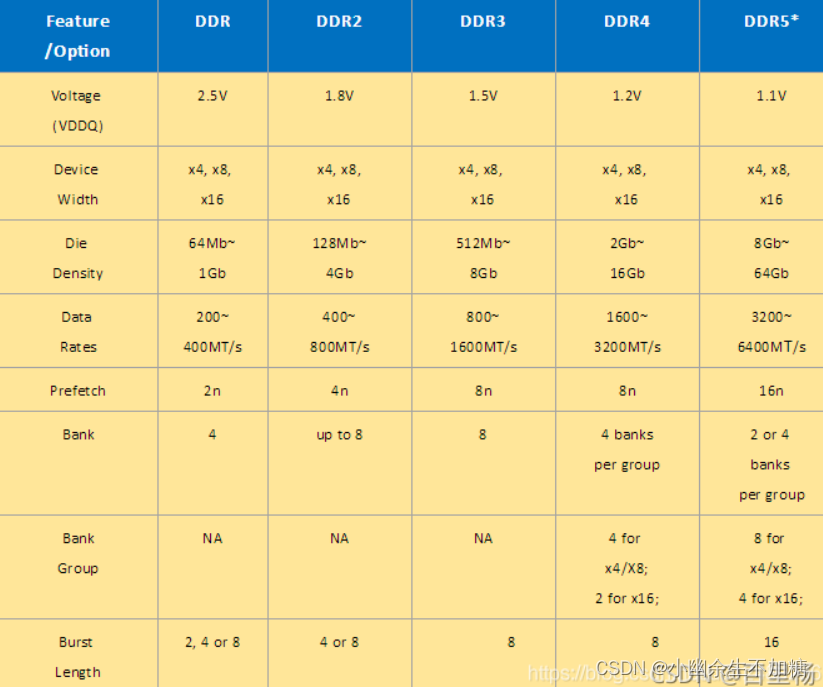

1.DIMM介绍

2.DDR2介绍

3.DDR3介绍

4.DDR4介绍

5.DDR5介绍

1.DIMM介绍

之前老说到DDR和SDRAM,提到过DIMM,那么什么是DIMM呢?

DIMM是指针脚插槽,也就是物理结构方面的分类;而SDRAM和DDR都是内部技术方面的分类。

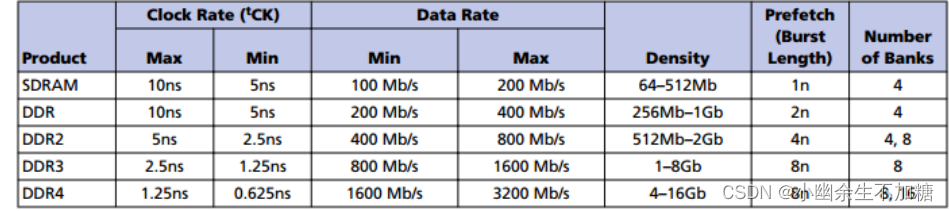

SDRAM:Synchronous Dynamic Random Access Memory,同步动态随机存储器。

而DDR(Double Data Rate)系列,严格意义上讲,应该是Double Data Rate SDRAM内存,也就是和说在SDRAM基础上改进的版本,只不过日常生活中,通常被简略的直接称作DDR内存。而无论是SDRAM还是DDR,实际上都是DIMM内存。

那么什么是DIMM内存呢?

DIMM(Dual Inline Memory Module,双列直插内存模块),是在单列直插存储器模块(single inline memory module,SIMM)的基础上发展起来的,SIMM提供32位数据通道,而DIMM则提供了64位的数据通道。

与SIMM不同的是DIMM的金手指两端不像SIMM那样是互通的,它们各自独立传输信号,因此可以满足更多数据信号的传送需要。

同样采用DIMM,SDRAM 的接口与DDR内存的接口也略有不同,SDRAM DIMM为168Pin DIMM结构,金手指每面为84Pin,金手指上有两个卡口,用来避免插入插槽时,错误将内存反向插入而导致烧毁;DDR DIMM则采用184Pin DIMM结构,金手指每面有92Pin,金手指上只有一个卡口。

卡口数量的不同,是二者最为明显的区别。

DDR2 DIMM为240pin DIMM结构,金手指每面有120Pin,与DDR DIMM一样金手指上也只有一个卡口,但是卡口的位置与DDR DIMM稍微有一些不同,因此DDR内存是插不进DDR2 DIMM的,同理DDR2内存也是插不进DDR DIMM的,因此在一些同时具有DDR DIMM和DDR2 DIMM的主板上,不会出现将内存插错插槽的问题。

为了满足笔记本电脑对内存尺寸的要求,SO-DIMM(Small Outline DIMM Module)也开发了出来,它的尺寸比标准的DIMM要小很多,而且引脚数也不相同。同样SO-DIMM也根据SDRAM和DDR内存规格不同而不同,SDRAM的SO-DIMM只有144pin引脚,而DDR的SO-DIMM拥有200pin引脚。此外笔记本内存还有MicroDIMM和Mini Registered DIMM两种接口。MicroDIMM接口的DDR为172pin,DDR2为214pin;Mini Registered DIMM接口为244pin,主要用于DDR2内存。DDR3 SO-DIMM接口为204pin;DDR4 SO-DIMM接口为260pin。

2.DDR2介绍

DDR2/DDR II(Double Data Rate 2)SDRAM是由JEDEC(电子设备工程联合委员会)进行开发的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同就是,虽然同是采用了在时钟的上升/下降沿同时进行数据传输的基本方式,但DDR2内存却拥有两倍以上一代DDR内存预读取能力(即:4bit数据读预取)。换句话说,DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。

由于DDR2标准规定所有DDR2内存均采用FBGA封装形式,而不同于广泛应用的TSOP/TSOP-Ⅱ封装形式,FBGA封装可以提供了更为良好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的发展提供了坚实的基础。

封装

DDR2内存技术最大的突破点其实不在于用户们所认为的两倍于DDR的传输能力,而是在采用更低发热量、更低功耗的情况下,DDR2可以获得更快的频率提升,突破标准DDR的400MHZ限制。

DDR内存通常采用TSOP芯片封装形式,这种封装形式可以很好的工作在200MHz上,当频率更高时,它过长的管脚就会产生很高的阻抗和寄生电容,这会影响它的稳定性和频率提升的难度。这也就是DDR的核心频率很难突破275MHZ的原因。而DDR2内存均采用FBGA封装形式。不同于广泛应用的TSOP封装形式,FBGA封装提供了更好的电气性能与散热性,为DDR2内存的稳定工作与未来频率的发展提供了良好的保障。

DDR2内存采用1.8V电压,相对于DDR标准的2.5V,降低了不少,从而提供了明显的更小的功耗与更小的发热量,这一点的变化是意义重大的。

双通道内存

需要INTEL芯片组的支持,内存的CAS延迟、容量需要相同。

不过,INTEL的弹性双通道的出现使双通道的形成条件更加宽松,不同容量的内存甚至都能组建双通道

除了以上所说的区别外,DDR2还引入了三项新的技术,它们是OCD、ODT和Post CAS。

离线驱动

OCD(Off-Chip Driver):也就是所谓的离线驱动调整,DDR Ⅱ通过OCD可以提高信号的完整性。DDR Ⅱ通过调整上拉(pull-up)/下拉(pull-down)的电阻值使两者电压相等。使用OCD通过减少DQ-DQS的倾斜来提高信号的完整性;通过控制电压来提高信号品质。

终端电阻器

ODT:ODT是内建核心的终端电阻器。我们知道使用DDR SDRAM的主板上面为了防止数据线终端反射信号需要大量的终结电阻。它大大增加了主板的制造成本。实际上,不同的内存模组对终结电路的要求是不一样的,终结电阻的大小决定了数据线的信号比和反射率,终结电阻小则数据线信号反射低但是信噪比也较低;终结电阻高,则数据线的信噪比高,但是信号反射也会增加。因此主板上的终结电阻并不能非常好的匹配内存模组,还会在一定程度上影响信号品质。DDR2可以根据自己的特点内建合适的终结电阻,这样可以保证最佳的信号波形。使用DDR2不但可以降低主板成本,还得到了最佳的信号品质,这是DDR不能比拟的。

利用效率

Post CAS:它是为了提高DDR Ⅱ内存的利用效率而设定的。在Post CAS操作中,CAS信号(读写/命令)能够被插到RAS信号后面的一个时钟周期,CAS命令可以在附加延迟(Additive Latency)后面保持有效。原来的tRCD(RAS到CAS和延迟)被AL(Additive Latency)所取代,AL可以在0,1,2,3,4中进行设置。由于CAS信号放在了RAS信号后面一个时钟周期,因此ACT和CAS信号永远也不会产生碰撞冲突。 采用双通道运行,速度是DDR的2倍。 总的来说,DDR2采用了诸多的新技术,改善了DDR的诸多不足,虽然它目前有成本高、延迟慢能诸多不足,但相信随着技术的不断提高和完善,这些问题终将得到解决。

技术特点

DDR2引入了三项新的技术,它们是OCD、ODT和PostCAS。

OCD(Off-ChipDriver):也就是所谓的离线驱动调整。

ODT:ODT是内建核心的终结电阻器。

PostCAS:它是为了提高DDR2内存的利用效率而设定的。

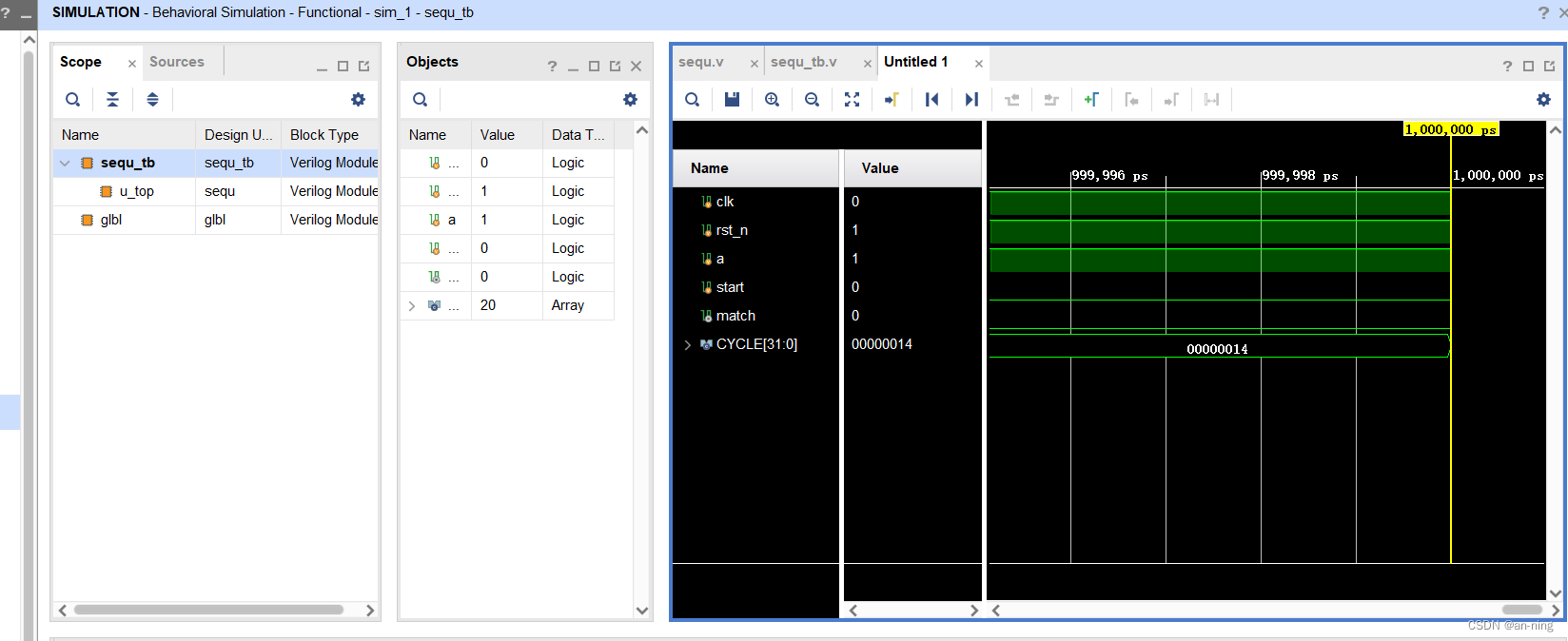

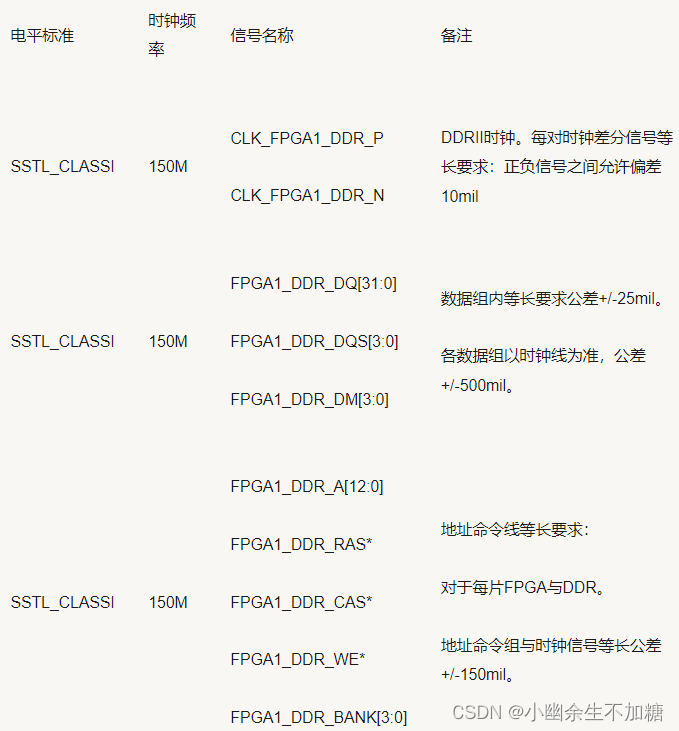

走线规则

时钟线包括 MEM_CLKOUT#0、MEM_CLKOUT0、MEM_CLKOUT#1、MEM_CLKOUT1,MEM_CLKOUT#2、MEM_CLKOUT2; MEM_CLKOUT#3、MEM_CLKOUT3、MEM_CLKOUT#4、MEM_CLKOUT4、MEM_CLKOUT#5、MEM_CLKOUT5。

DDR2时钟线走线规则 分线对与对之间的间距为20mil min;

DDR时钟线对其他线的间距为20mil min;

北桥Breakout出来4mil,差分线对内间距6mil min,长度控制1000mil以内。再出来线宽6.5mil,差分线对内两根线的间距为5mils,蛇形线间距为20mils;

DDR2时钟线走线长度约束规则 差分线对内两根线±10mils;

每个DIMM三对差分线匹配在50mils内,即最大值减最小值不大于50mils;所有线长在2850mils和6500mils间

阻抗控制: 70Ω±10%(差分线)

DDR等长约束

3.DDR3介绍

DDR3是一种计算机内存规格。它属于SDRAM家族的内存产品,提供了相较于DDR2 SDRAM更高的运行效能与更低的电压,是DDR2 SDRAM(同步动态动态随机存取内存)的后继者(增加至八倍),也是现时流行的内存产品规格。

CWD是作为写入延迟之用,Reset提供了超省电功能的命令,可以让DDR3 SDRAM内存颗粒电路停止运作、进入超省电待命模式,ZQ则是一个新增的终端电阻校准功能,新增这个线路脚位提供了ODCE(On Die Calibration Engine)用来校准ODT(On Die Termination)内部终端电阻,新增了SRT(Self-Reflash Temperature)可编程化温度控制内存时脉功能,SRT的加入让内存颗粒在温度、时脉和电源管理上进行优化,可以说在内存内,就做了电源管理的功能,同时让内存颗粒的稳定度也大为提升,确保内存颗粒不致于工作时脉过高导致烧毁的状况,同时DDR3 SDRAM还加入PASR(Partial Array Self-Refresh)局部Bank刷新的功能,可以说针对整个内存Bank做更有效的资料读写以达到省电功效。

与DDR2相比的新设计

1.8bit预取设计,而DDR2为4bit预取,这样DRAM内核的频率只有等效数据频率的1/8,DDR3-800的核心工作频率(内核频率)只有100MHz。

2.采用点对点的拓扑架构,以减轻地址/命令与控制总线的负担。

3.采用100nm以下的生产工艺,将工作电压从DDR2的1.8V降至1.5V,增加异步重置(Reset)与ZQ校准功能。

与DDR2相比

1.突发长度(Burst Length,BL):由于DDR3的预取为8bit,所以突发传输周期(Burst Length,BL)也固定为8,而对于DDR2和早期的DDR架构系统,BL=4也是常用的,DDR3为此增加了一个4bitBurst Chop(突发突变)模式,即由一个BL=4的读取操作加上一个BL=4的写入操作来合成一个BL=8的数据突发传输,届时可通过A12地址线来控制这一突发模式。而且需要指出的是,任何突发中断操作都将在DDR3内存中予以禁止,且不予支持,取而代之的是更灵活的突发传输控制(如4bit顺序突发)。

2.寻址时序(Timing):就像DDR2从DDR转变而来后延迟周期数增加一样,DDR3的CL周期也将比DDR2有所提高。DDR2的CL范围一般在2~5之间,而DDR3则在5~11之间,且附加延迟(AL)的设计也有所变化。DDR2时AL的范围是0~4,而DDR3时AL有三种选项,分别是0、CL-1和CL-2。另外,DDR3还新增加了一个时序参数——写入延迟(CWD),这一参数将根据具体的工作频率而定。

3.DDR3新增的重置(Reset)功能:重置是DDR3新增的一项重要功能,并为此专门准备了一个引脚。DRAM业界很早以前就要求增加这一功能,如今终于在DDR3上实现了。这一引脚将使DDR3的初始化处理变得简单。当Reset命令有效时,DDR3内存将停止所有操作,并切换至最少量活动状态,以节约电力。 在Reset期间,DDR3内存将关闭内在的大部分功能,所有数据接收与发送器都将关闭,所有内部的程序装置将复位,DLL(延迟锁相环路)与时钟电路将停止工作,而且不理睬数据总线上的任何动静。这样一来,将使DDR3达到最节省电力的目的。

4.DDR3新增ZQ校准功能:ZQ也是一个新增的脚,在这个引脚上接有一个240欧姆的低公差参考电阻。这个引脚通过一个命令集,通过片上校准引擎(On-Die Calibration Engine,ODCE)来自动校验数据输出驱动器导通电阻与ODT的终结电阻值。当系统发出这一指令后,将用相应的时钟周期(在加电与初始化之后用512个时钟周期,在退出自刷新操作后用256个时钟周期、在其他情况下用64个时钟周期)对导通电阻和ODT电阻进行重新校准。

5.参考电压分成两个:在DDR3系统中,对于内存系统工作非常重要的参考电压信号VREF将分为两个信号,即为命令与地址信号服务的VREFCA和为数据总线服务的VREFDQ,这将有效地提高系统数据总线的信噪等级。

6.点对点连接(Point-to-Point,P2P):这是为了提高系统性能而进行的重要改动,也是DDR3与DDR2的一个关键区别。在DDR3系统中,一个内存控制器只与一个内存通道打交道,而且这个内存通道只能有一个插槽,因此,内存控制器与DDR3内存模组之间是点对点(P2P)的关系(单物理Bank的模组),或者是点对双点(Point-to-two-Point,P22P)的关系(双物理Bank的模组),从而大大地减轻了地址/命令/控制与数据总线的负载。而在内存模组方面,与DDR2的类别相类似,也有标准DIMM(台式PC)、SO-DIMM/Micro-DIMM(笔记本电脑)、FB-DIMM2(服务器)之分,其中第二代FB-DIMM将采用规格更高的AMB2(高级内存缓冲器)。 面向64位构架的DDR3显然在频率和速度上拥有更多的优势,此外,由于DDR3所采用的根据温度自动自刷新、局部自刷新等其它一些功能,在功耗方面DDR3也要出色得多,因此,它可能首先受到移动设备的欢迎,就像最先迎接DDR2内存的不是台式机而是服务器一样。

性能上的特点

(1)功耗和发热量较小:吸取了DDR2的教训,在控制成本的基础上减小了能耗和发热量,使得DDR3更易于被用户和厂家接受。

(2)工作频率更高:由于能耗降低,DDR3可实现更高的工作频率,在一定程度弥补了延迟时间较长的缺点,同时还可作为显卡的卖点之一,这在搭配DDR3显存的显卡上已有所表现。

(3)降低显卡整体成本:DDR2显存颗粒规格多为16M X 32bit,搭配中高端显卡常用的128MB显存便需8颗。而DDR3显存颗粒规格多为32M X 32bit,单颗颗粒容量较大,4颗即可构成128MB显存。如此一来,显卡PCB面积可减小,成本得以有效控制,此外,颗粒数减少后,显存功耗也能进一步降低。

(4)通用性好:相对于DDR变更到DDR2,DDR3对DDR2的兼容性更好。由于针脚、封装等关键特性不变,搭配DDR2的显示核心和公版设计的显卡稍加修改便能采用DDR3显存,这对厂商降低成本大有好处。

4.DDR4介绍

DDR4 SDRAM(Double-Data-Rate Fourth Generation Synchronous Dynamic Random Access Memory,简称为DDR4 SDRAM),是一种高带宽的计算机存储器规格。它属于SDRAM家族的存储器产品,提供了相较于DDR3 SDRAM更高的运行性能与更低的电压,是现时最新的存储器规格。起始数据传送率由2133MT/s起跳,上限暂定为4266MT/s。

DDR的电源又可分为三类:

主电源VDD和VDDQ。

主电源的要求是VDDQ=VDD=1.2V。

VDDQ是给IO buffer供电的电源,VDD则是DDR的core power supply。一般使用中都是吧VDDQ和VDD合成一个电源使用,在SODIMM上则只有VDD引脚,内存条上可能有一些电路,也可能没有。

参考电源Vref。

参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,这个电压既可以使用电源芯片,也可以使用电阻分压的方式得到。

Vref电流较小,在几个mA-几十mA之间。一般采用电阻分压的方式,分压电阻在100~10K之间均可,需要1%精度的电阻。Vref的每个管教上需要加10nF的电容滤波,并且每个分压电阻上也并联一个电容较好。

匹配电压VTT(Tracking Termination Voltage)

VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。

DDR的设计中,有些用不到VTT;但如果使用VTT,VTT的电流要求是比较大的,因此需要专门的电源芯片来满足要求,并且会放一些uF级别储能电容。

激活电压VPP(DRAM Activating Power Supply)

VPP一般为2.5V。

VPP激活电压,必须要同时或者早于VDD,电压值也要全时间段都高于VDD。

时钟

DDR时钟CK_N/P为差分走线,一般使用终端并联100欧姆的匹配方式,差分走线差分对控制阻抗为差分100欧姆,单端50欧姆。

DDR4的工作时钟依赖于DDR controller的input,一般也即CPU或者交换芯片。

关于DDR4详情硬件设计参考博客:https://blog.csdn.net/sinat_15677011/article/details/113786705

DDR4 新增了4 个Bank Group 数据组的设计,各个Bank Group具备独立启动操作读、写等动作特性,Bank Group 数据组可套用多任务的观念来想象,亦可解释为DDR4 在同一频率工作周期内,至多可以处理4 笔数据,效率明显好过于DDR3。 另外DDR4增加了DBI(Data Bus Inversion)、CRC(Cyclic Redundancy Check)、CA parity等功能,让DDR4内存在更快速与更省电的同时亦能够增强信号的完整性、改善数据传输及储存的可靠性。

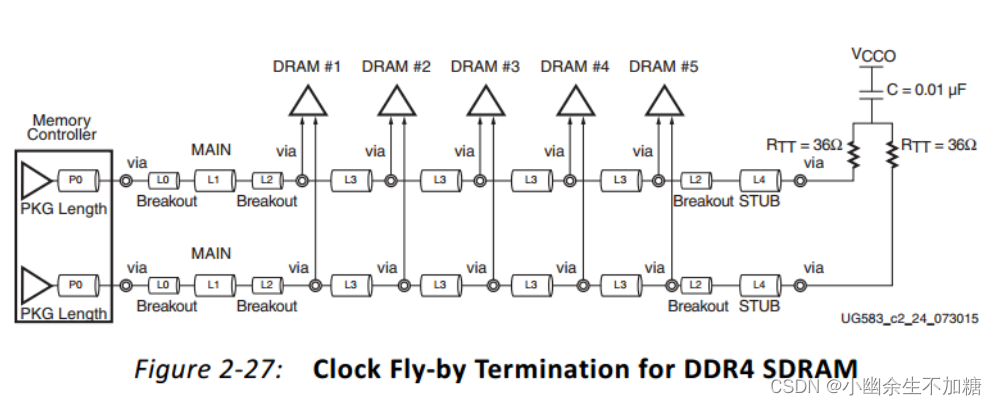

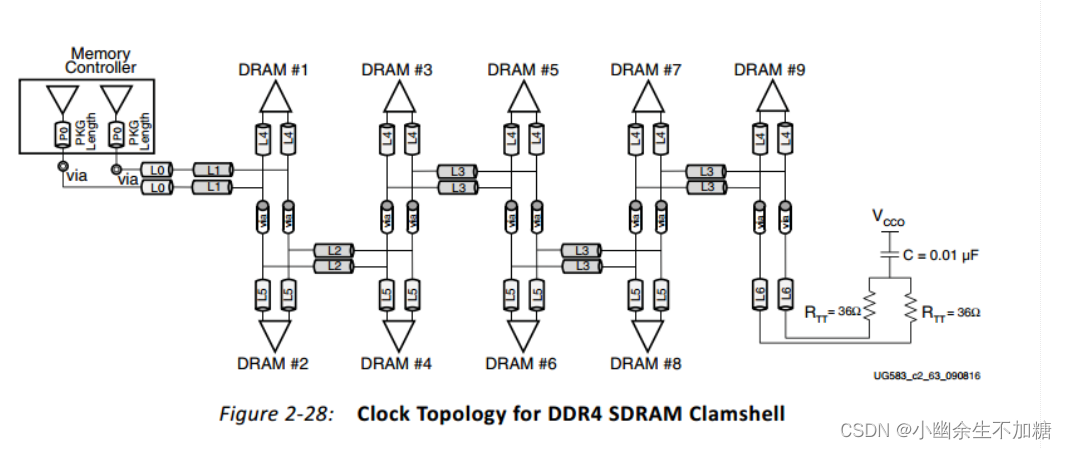

下面两张图分别为时钟信号(CK_T/CK_C)在 Fly-By 和 Clamshell 两种拓扑结构下走线及端接的示意图。

5.DDR5介绍

与DDR4内存相比,DDR5标准性能更强,功耗更低。其它变化还有,电压从1.2V降低到1.1V,同时每通道32/40位(ECC)、总线效率提高、增加预取的Bank Group数量以改善性能等。目前还没有正式支持DDR5内存的平台,AMD预计会在2021年的Zen4处理器上更换插槽,支持DDR5内存,而Intel这边14nm及10nm处理器都没有明确过DDR5内存支持,官方路线图显示2021年的7nm工艺Sapphire Rapids处理器才会上DDR5,而且是首发服务器产品,消费级的估计还要再等等。

Cadence表示,与DDR4相比,改进的DDR5功能将使实际带宽提高36%,即使在3200 MT / s(此声明必须进行测试)和4800 MT / s速度开始,与DDR4-3200相比,实际带宽将高出87%。与此同时,DDR5最重要的特性之一将是超过16 Gb的单片芯片密度。

主要特性

等效频率提升

大家最能感受到的等效频率的提升,直接从“2133MHz”增长至“4800MHz”,随着当下DDR5内存调参的深入,6400MHz或将成为主流水平。

频率的提升,使得DDR5内存在理论跑分上有了提升,在读取测试、写入测试,还是复制、延时方面,从跑分结果而言提升较大。

DRAM容量提升

内存的DRAM容量也是此次DDR5内存技术提升的重点方向,在JEDEC的DDR4规范中,单颗内存Die最大容量只有16Gb,而到了DDR5时代,单颗Die的容量上到64Gb的高度。

工作电压更低

DDR5内存工作电压低至1.1V,对比DDR4最低1.2V的工作电压,实现了20%左右的降低,它的降低拥有两个重要意义。

其一是功耗方面,尤其是对于笔记本产品,以及企业级服务器产品而言,20%的功耗降低,具有显著的节能意义;其二是超频潜能,起始电压的降低,使得后续进行超频调参有了更大的可操作空间,能进一步提升内存的超频潜能。

On-die ECC

引入ECC纠错机制,从而规避风险,提高可靠性并降低缺陷率。

双32位寻址通道

双32位寻址通道的引入,其基本原理是将DDR5内存模组内部64位数据带宽,分为两路带宽分别为32位的可寻址通道,从而有效的提高了内存控制器,进行数据访问的效率,同时减少了延迟。

参考资料:

[1]百度百科

[2]http://www.wangdali.net/ddr4/

[3]JESD79-4A-(DDR4)

[4]https://www.sohu.com/a/155021909_463982

[5]https://blog.csdn.net/jiangchao3392/article/details/104030028

![低成本实现webhook接收端[python]](https://img-blog.csdnimg.cn/54bc116f36854618968a53133c34aa2c.png#pic_center)