文章目录

- 数组逻辑设计(4)

- 1. 组合逻辑电路中的险象

- 一、门延迟

- 二、逻辑冒险

- 三、险象的分类

- 1)静态冒险

- 2)动态冒险

- 3)功能冒险

- 2. 险象的判断及消除

- 险象的判断

- 1)代数法

- 2) 卡诺图法

- 险象的消除

- 1)在切点处添加卡诺圈

- 2)添加冗余项

- 3)添加吸收电容

- 4)加封锁/选通脉冲

- 3. 组合逻辑电路的测试

数组逻辑设计(4)

1. 组合逻辑电路中的险象

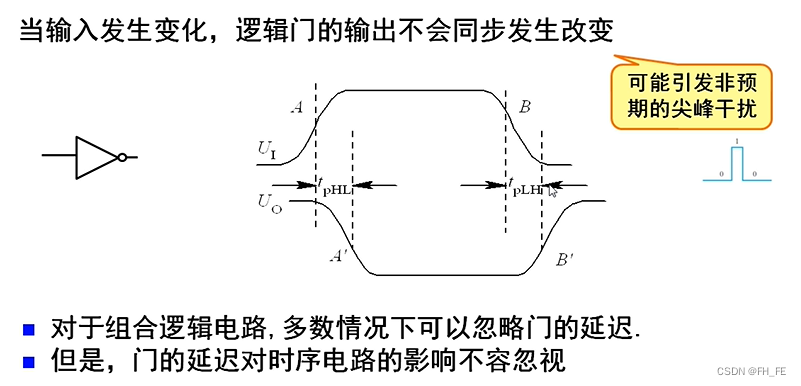

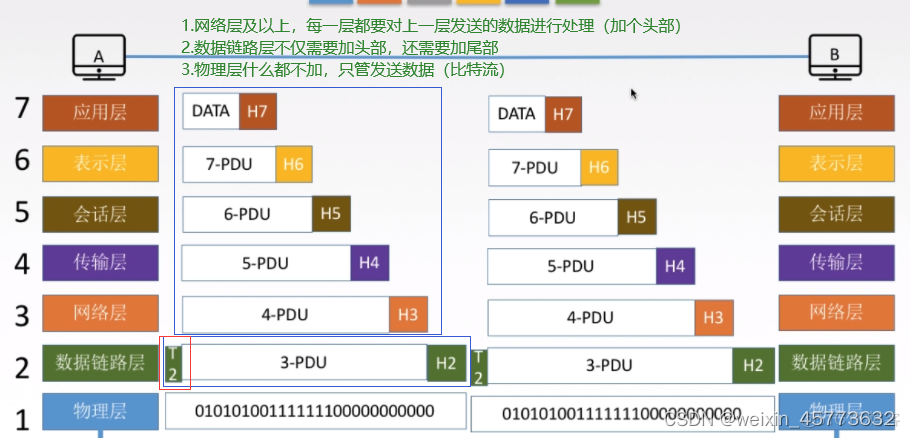

一、门延迟

控制端输入发生变化时,逻辑门的输出变化会有一定的延时,可能会引发非预期的尖峰干扰

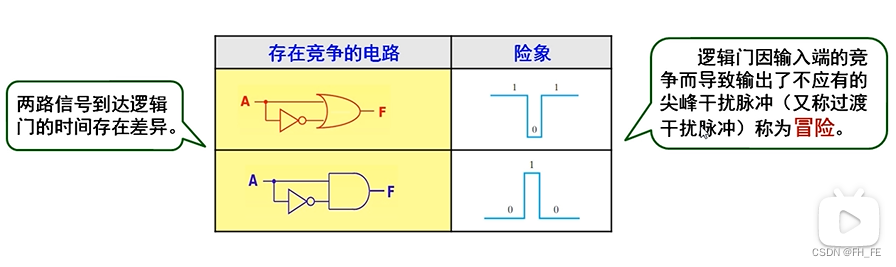

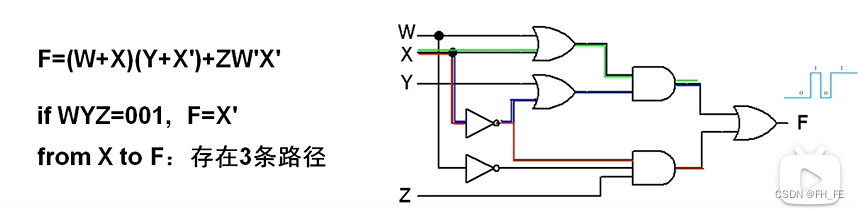

二、逻辑冒险

当一个逻辑门的两个输入端的信号同时向相反方向变化,则该电路存在竞争

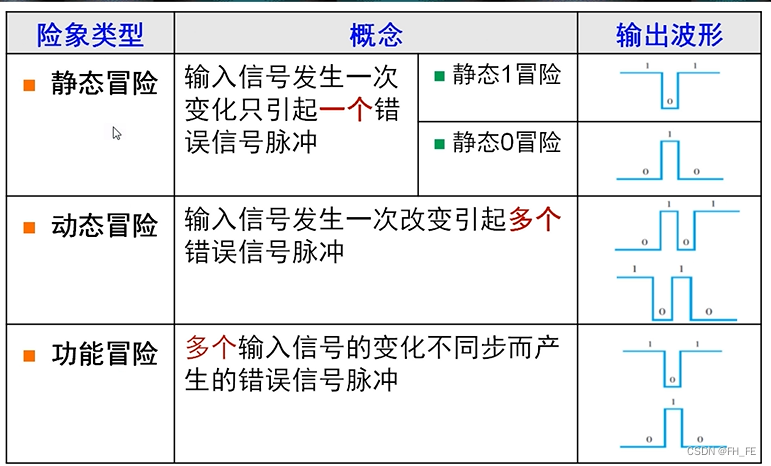

三、险象的分类

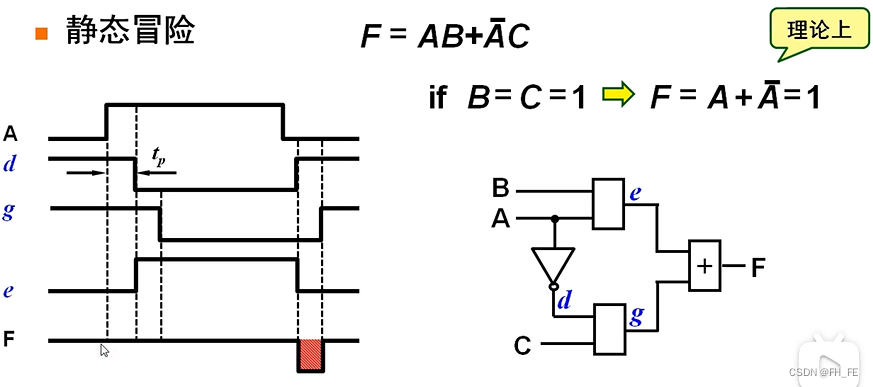

1)静态冒险

例1:

理论上F=A+A‾F=A+\overline{A}F=A+A输出结果恒为1,但是由于静态冒险的存在,会有错误信号输出,过程如下:

刚开始,A=0,d=1, e=0, g=1, F = 1

d端有个非门,对信号传输造成一定的延时,出现

(1)A=1, e=1, d=0, 延时导致g=1,输出F=1

(2)A=1, e=1, d=0, g=0, F=1

(3)A=0, e=0, d=0, 延时导致g=0, 输出F=0

(4)A=0, e=0, d=0, g=1, 输出F=0

第三个环节中静态冒险导致了非预期的尖峰干扰,出现了输出低电平的瞬间

例2

2)动态冒险

1.通常发生在多级电路中

2.不同的路径有不同的传输延迟

3. 当输入发生一次变化,输出将发生多次变化

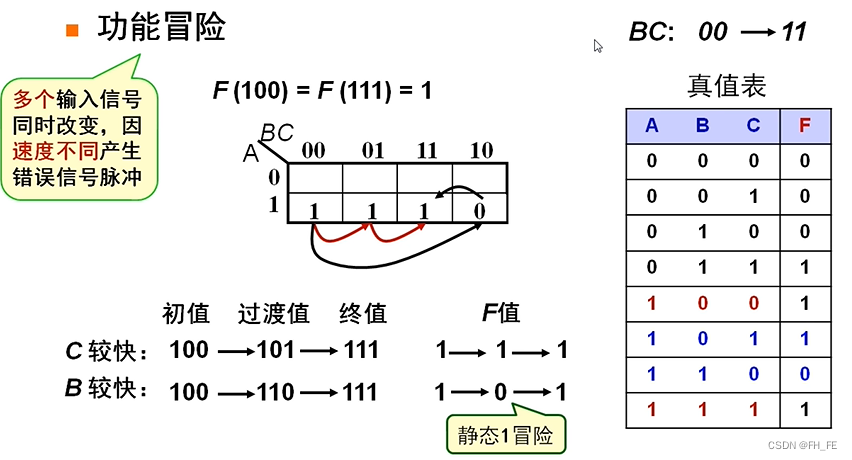

3)功能冒险

多个输入信号同时改变,因速度不同产生错误信号脉冲

2. 险象的判断及消除

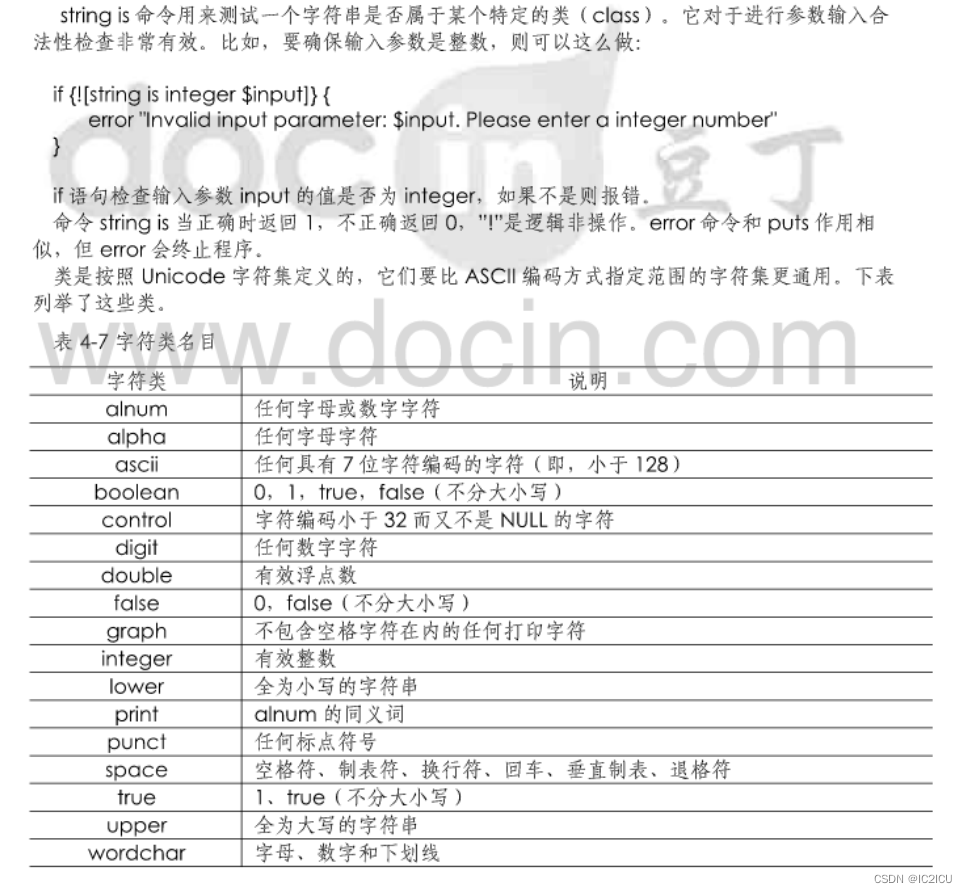

险象的判断

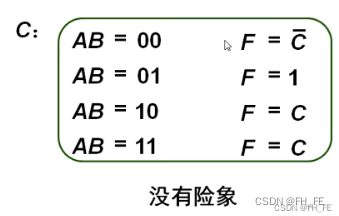

1)代数法

例1

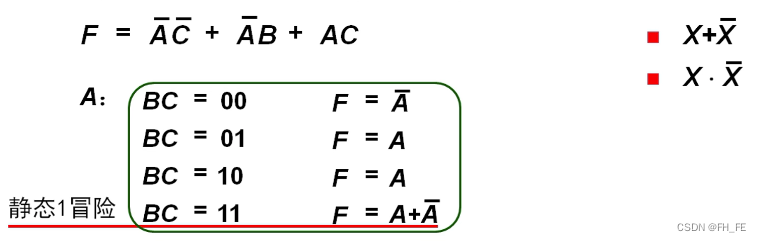

上图中表达式F=A‾C‾+A‾B+ACF = \overline{A}\space\overline{C} + \overline{A}B + ACF=A C+AB+AC中没有B‾\overline{B}B所以不可能关于B出现险象,只需检查A和C即可

首先检查C,将ABABAB分别取所有可能,检查输出F没有险象出现

再检查A,取BCBCBC的所有可能,查看输出,发现当BC=11BC=11BC=11时出现静态1冒险

例2

上式中没有C‾\overline{C}C只需要检查AB即可

首先检查A,当BC=00BC=00BC=00时,F=AA‾F=A\overline{A}F=AA

存在静态0冒险

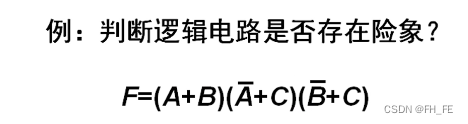

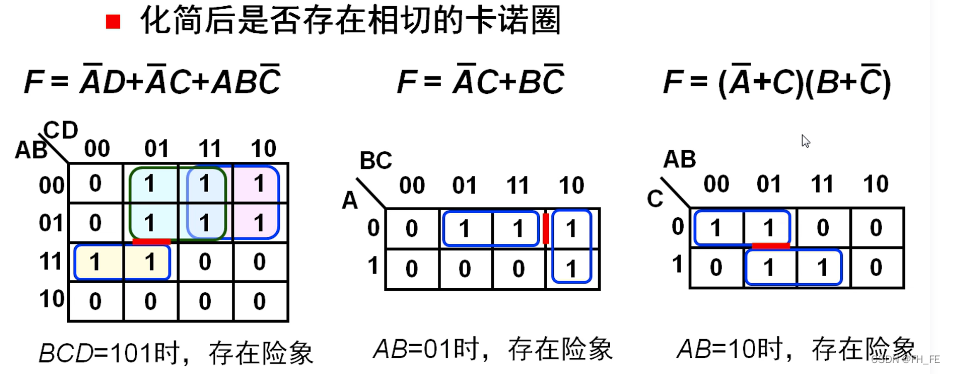

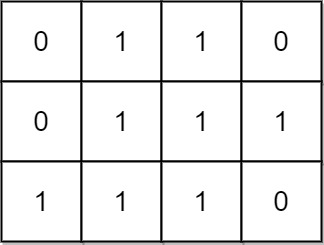

2) 卡诺图法

化简之后画出卡诺圈,判断是否存在相切的卡诺圈,如果存在相切情况,则存在险象

险象的消除

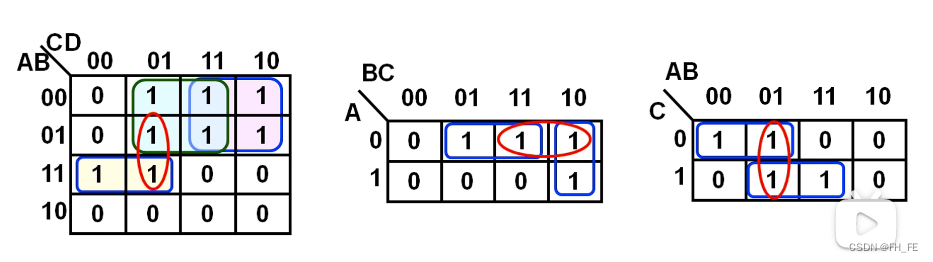

1)在切点处添加卡诺圈

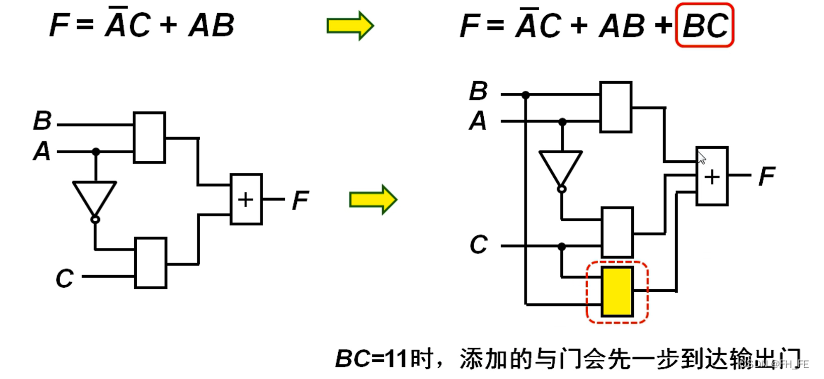

2)添加冗余项

利用逻辑代数的知识,在表达式中添加冗余项,该冗余项的作用就是在电路中添加一个与门,让高电平信号能够i及时到达或门

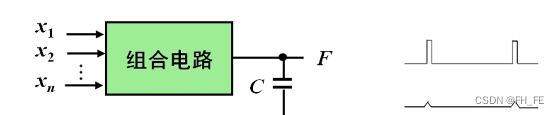

3)添加吸收电容

在接收端添加一个电容,吸收尖峰电平,达到了消除险象的作用

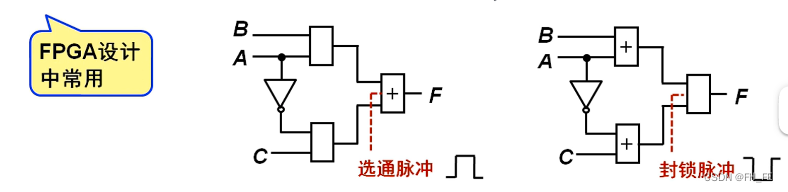

4)加封锁/选通脉冲

不需要额外添加逻辑门,只需要在输出端添加一个选通脉冲(或门)或者封锁脉冲(与门)即可通过高低电平选择达到消除险象的目的。常用在FPGA设计中。

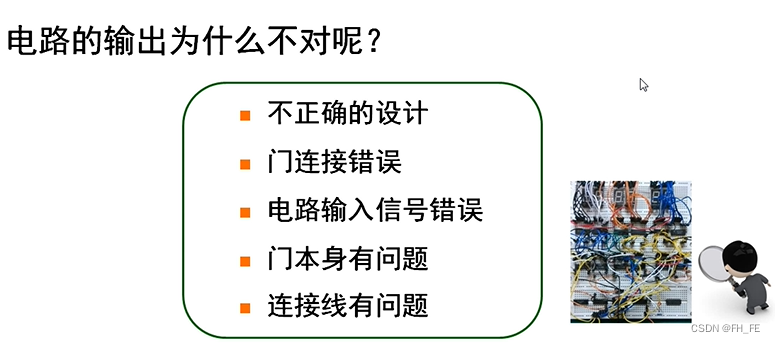

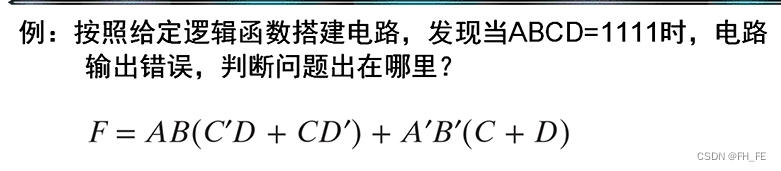

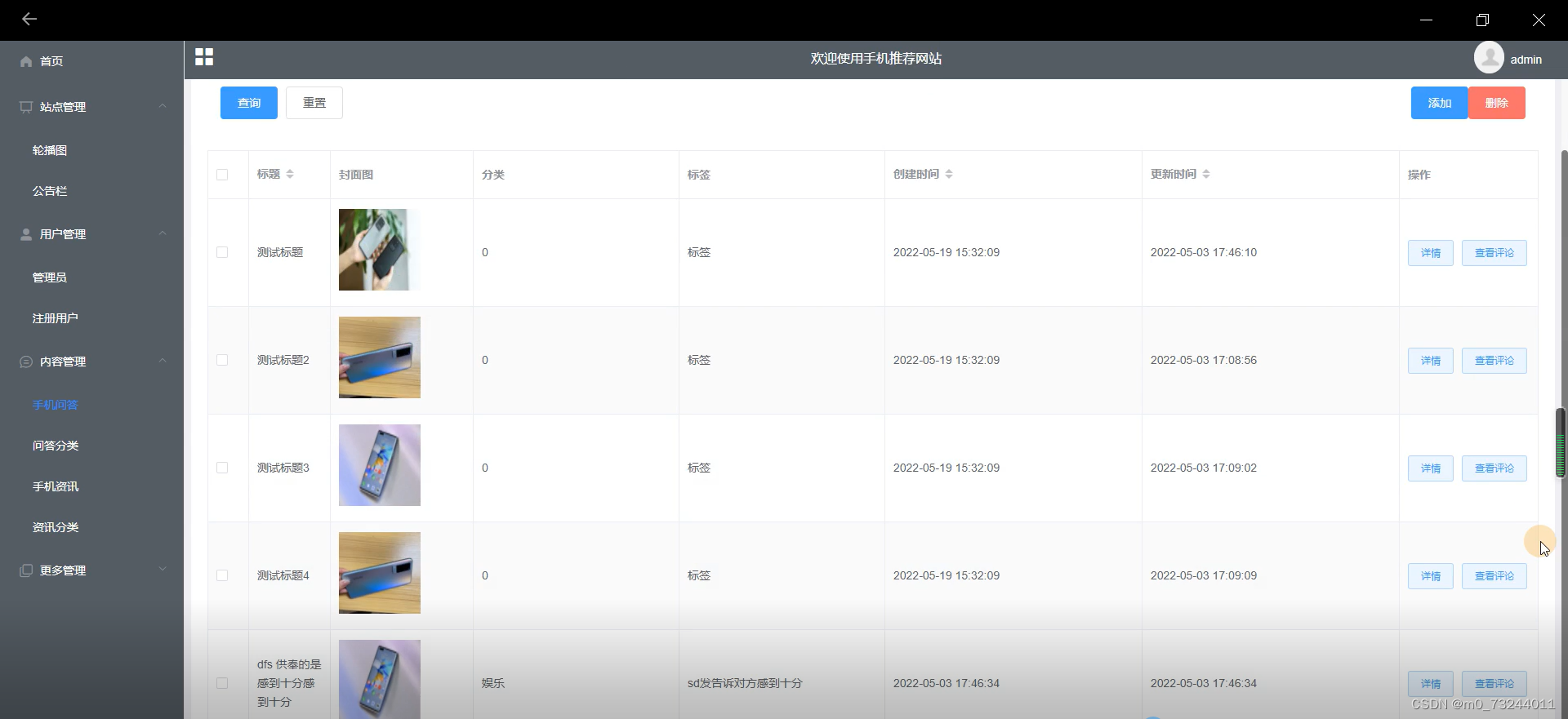

3. 组合逻辑电路的测试

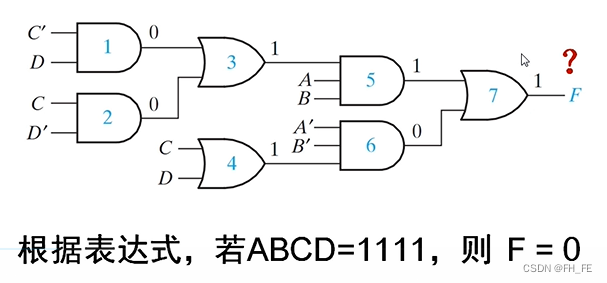

例1

首先带入ABCD=1111ABCD=1111ABCD=1111,发现表达式的输出和逻辑电路的输出不同, 说明电路设计有问题

下面进行问题分析

问题分析的过程要从输出端开始,逐步向输入端排查

1)首先输出应该是0,输出端错误,可能是七号门的输入有问题,或者七号门本身有问题

2)检查发现七号门和五号门相连的信号输入错误,应该是0,那么问题很可能出在5号门及其输入上

3)检查五号门的运算过程并无错误,所以可能是5五号门输入及其之前门电路的问题

4)检查发现三号门的计算过程有问题,可能是三号门本身或者其输入的问题

5)检查发现一号、二号门的运算过程并无问题,问题定位到三号门及其输入端

结论: 三号门本身有问题,或者其输入的数据线有问题(接口没插牢,数据线损坏等)

观察ppt中的错误排查方法,对所有器件进行了排查,更为严谨

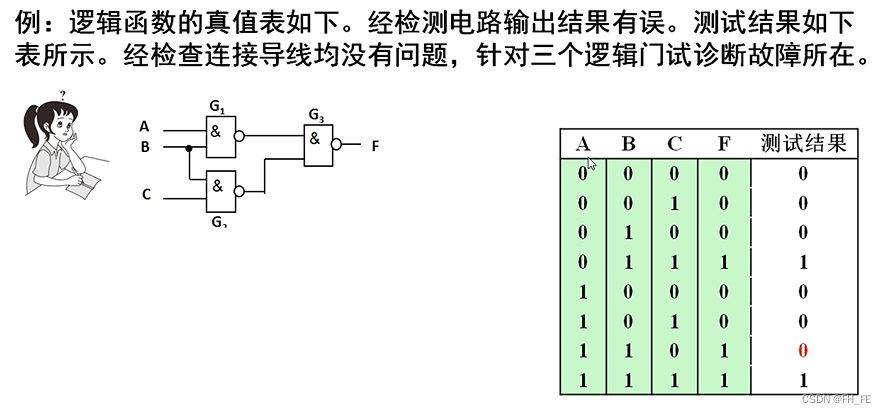

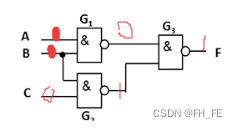

例2

如果正常运算,过程应该如下

但是输出结果为0,则说明G3有问题或者其输入为两个1

如果输入为两个1,则G1有问题,可能是非门故障

结论: G1或G3有问题

![[Java]快速入门二叉树,手撕相关面试题](https://img-blog.csdnimg.cn/79a615f6390b4c358ee4402f94b819ae.jpeg)