OrCAD原理图检查

- FPGA或处理器芯片原理图封装检查

- OrCad元件Part Reference与Reference位号不同

- 检查所有器件是否与CIS库元件匹配

- 用CIS库中的元器件替换已存在器件

- 方法1

- 方法2

- DRC检查

- 修改页码

- Annotate重排位号

- 利用Intersheet References功能进行off-page索引

- 检查封装、厂家、型号等信息

- 运行DRC

- 生成网表异常

- 提示冲突值

- 基于CIS库生成bom

- OrCad原理图比较工具

- Allegro中进行网表比较

- Allegro配合进行原理图网络逐个检查

- 检查表

FPGA或处理器芯片原理图封装检查

绘制完成的封装应放置在一张空白原理图中,并选择所有part,点击右键->编辑属性->pin,将Pin Number、Pin Name和网络名(看需要)三列拷贝到Excel表格中,并用比较软件(Beyond Compare 3)和官网提供的pin-out表格进行对比,应完全相同。

OrCad元件Part Reference与Reference位号不同

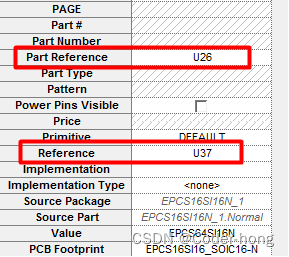

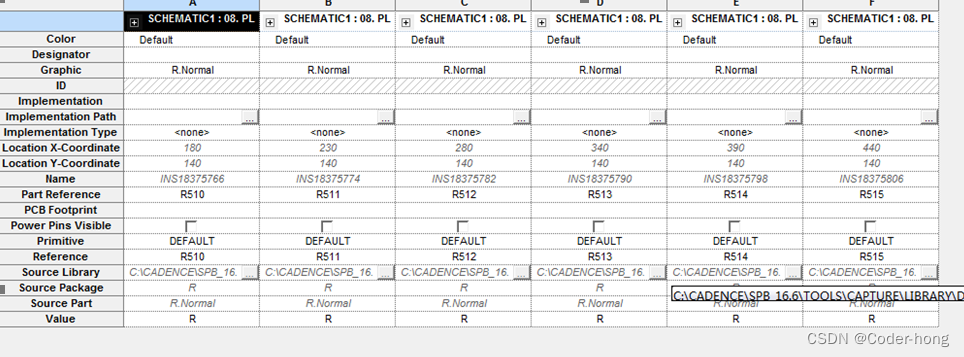

如下图所示:

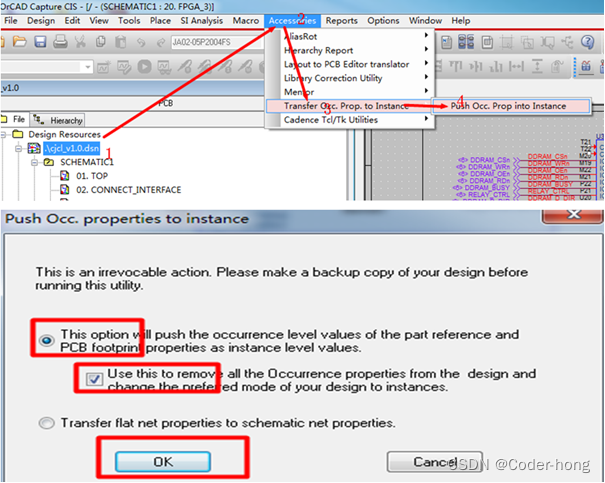

按照如下方法,删除强制属性,操作前需对DSN设计文件进行备份,防止不可恢复的错误发生。

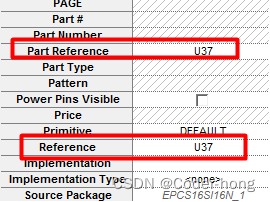

删除以后,强制属性均被删除,由增量属性替代,如下图所示:

检查所有器件是否与CIS库元件匹配

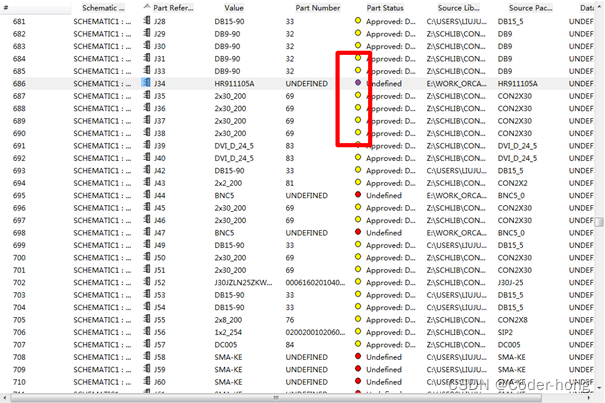

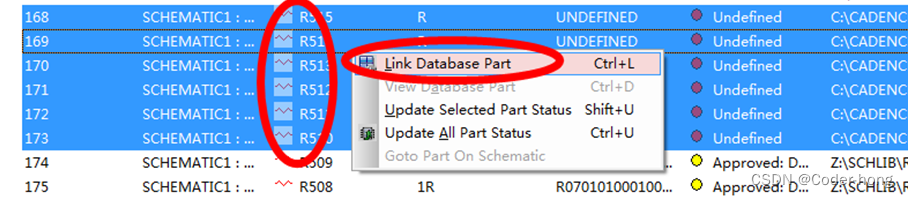

在DSN文件上点右键,选择“Part Manager”,如下图,在Part Status列标红为不匹配元器件:

用CIS库中的元器件替换已存在器件

方法1

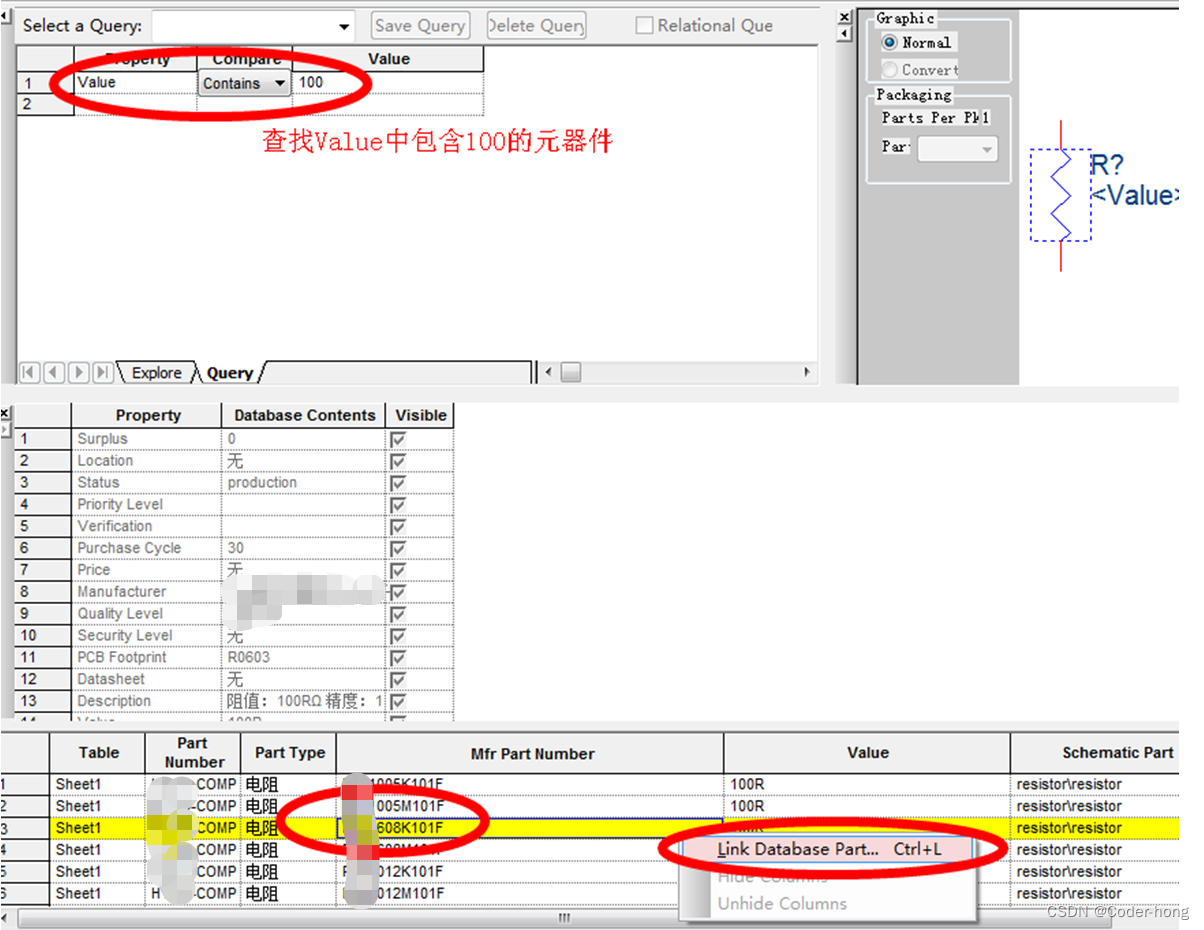

在DSN文件上点右键,选择“Part Manager”,在元器件管理窗口选中需要替换的元器件(可按Ctrl或Shift多选),点右键选择“Link Database Part”,在CIS库管理界面查找将要选用的元器件,如下图,然后在待选器件上点右键选择“Link Database Part”。

- 查看待替换器件属性:

- 连接数据库器件:

- 在数据库中寻找合适的器件,并进行连接:

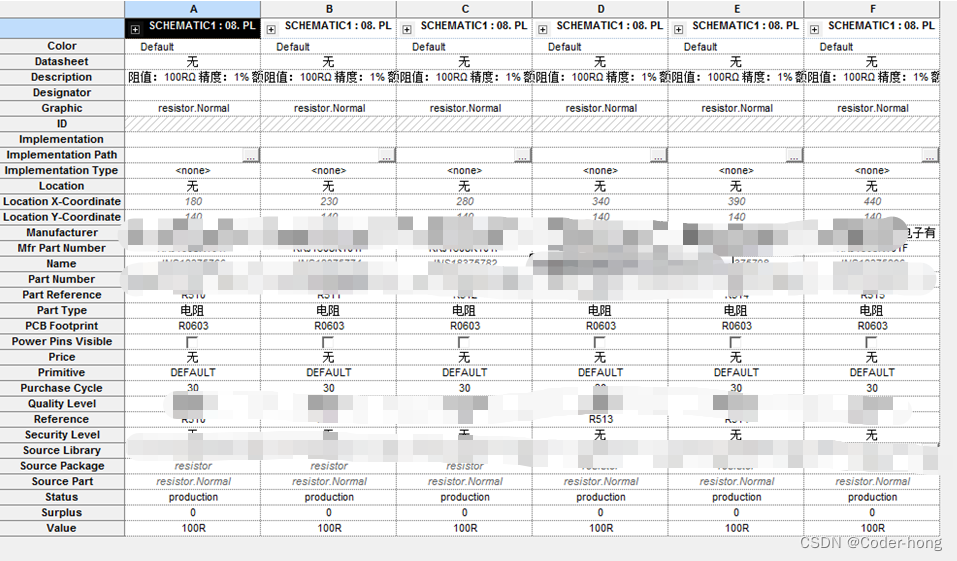

- 确认替换后的器件属性:

方法2

直接在原理图中右键点击需要替换的元器件,并点选择“Link Database Part”,后续步骤与方法1相同。

DRC检查

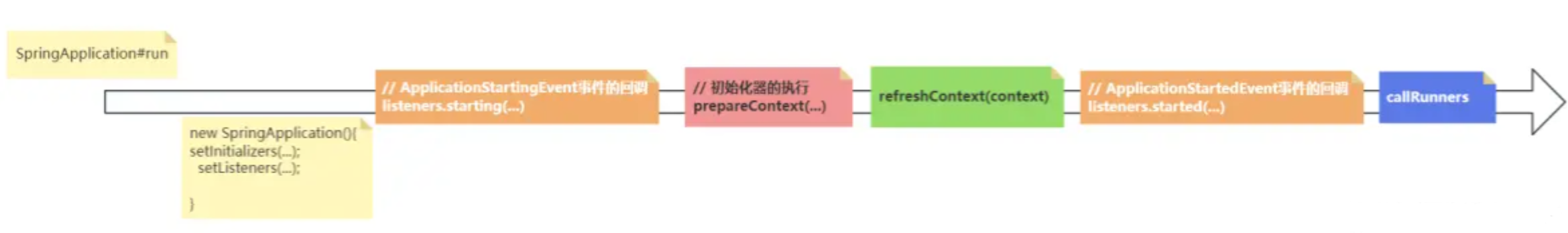

利用Orcad软件自带的DRC等功能可有效地检查发现原理图绘制过程中操作失误产生的问题,下面分三步进行原理图检查。

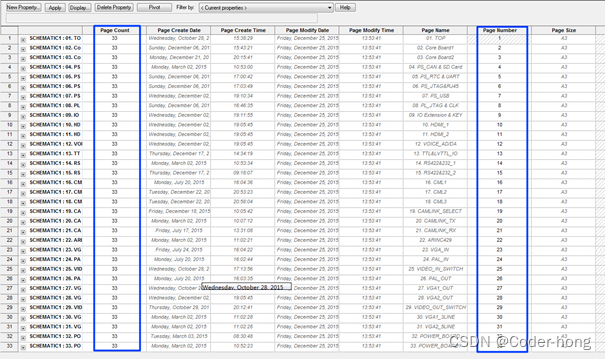

修改页码

首先需要修改每页的页码,工程管理器->右键点击.dsn文件->Edit Object Properties->Title Blocks标签->点击表格左上角垂直排序如下图所示:

**技巧:**此处,可进行表格复制、粘贴等操作,即可以在Excel中进行增量填充,并直接粘贴进来。

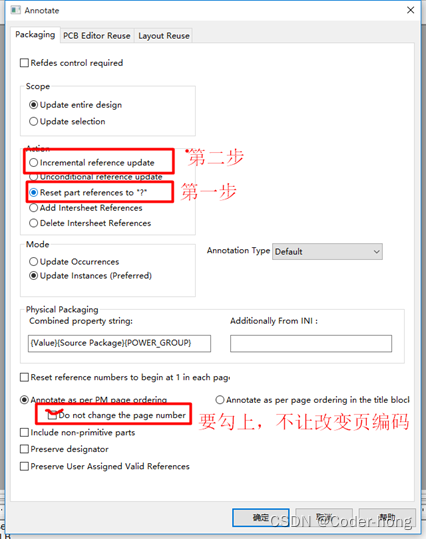

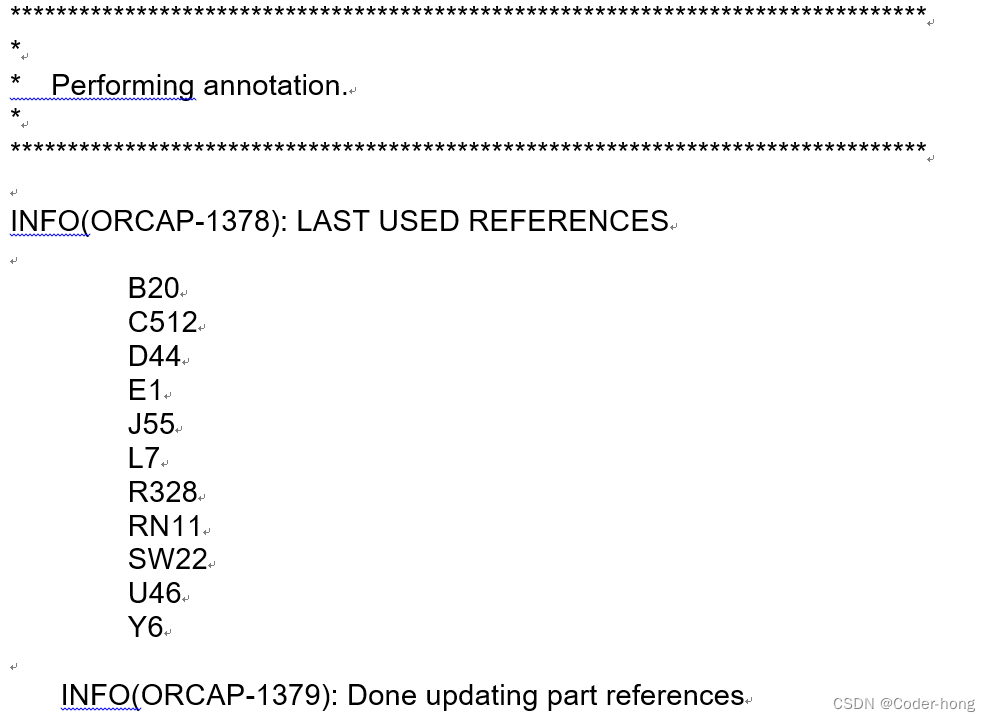

Annotate重排位号

利用Annotate功能进行元器件位号重排,如下图所示,可修正编号重复,和编号无规律的问题。查看日志文件,是否有不常规的命名方式,并能够看出每种位号的总数。

日志:

SW22则表示SW开头的位号共22个元件

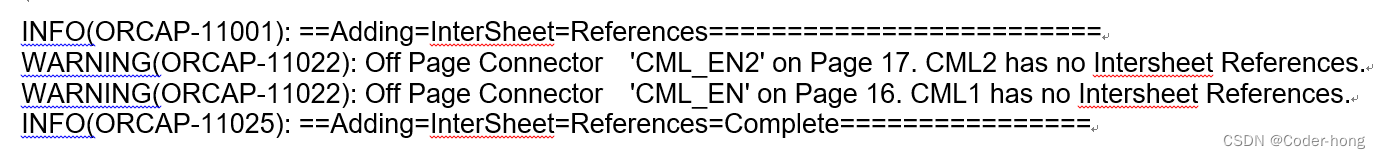

利用Intersheet References功能进行off-page索引

索引完成后需检查log,看是否有页间独立网络标号等。

下面的日志表示:CML_EN2和CML_EN网络独立,没有与其他页网络相连。

**技巧:**点击 Edit->Clear Session Log可清除日志记录

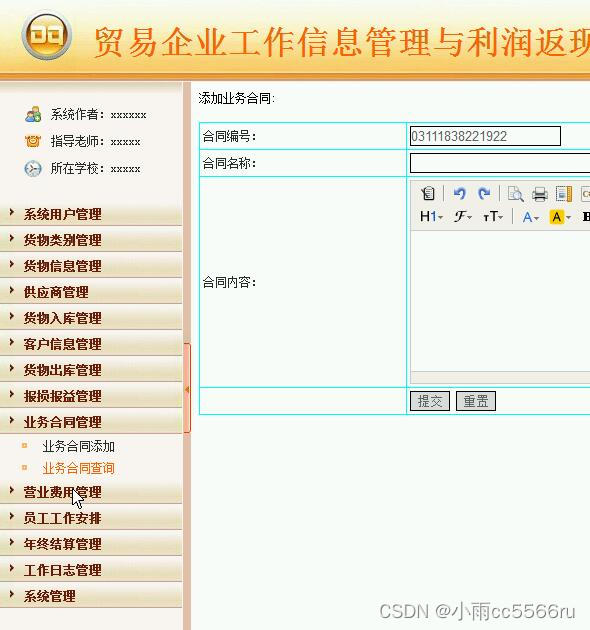

检查封装、厂家、型号等信息

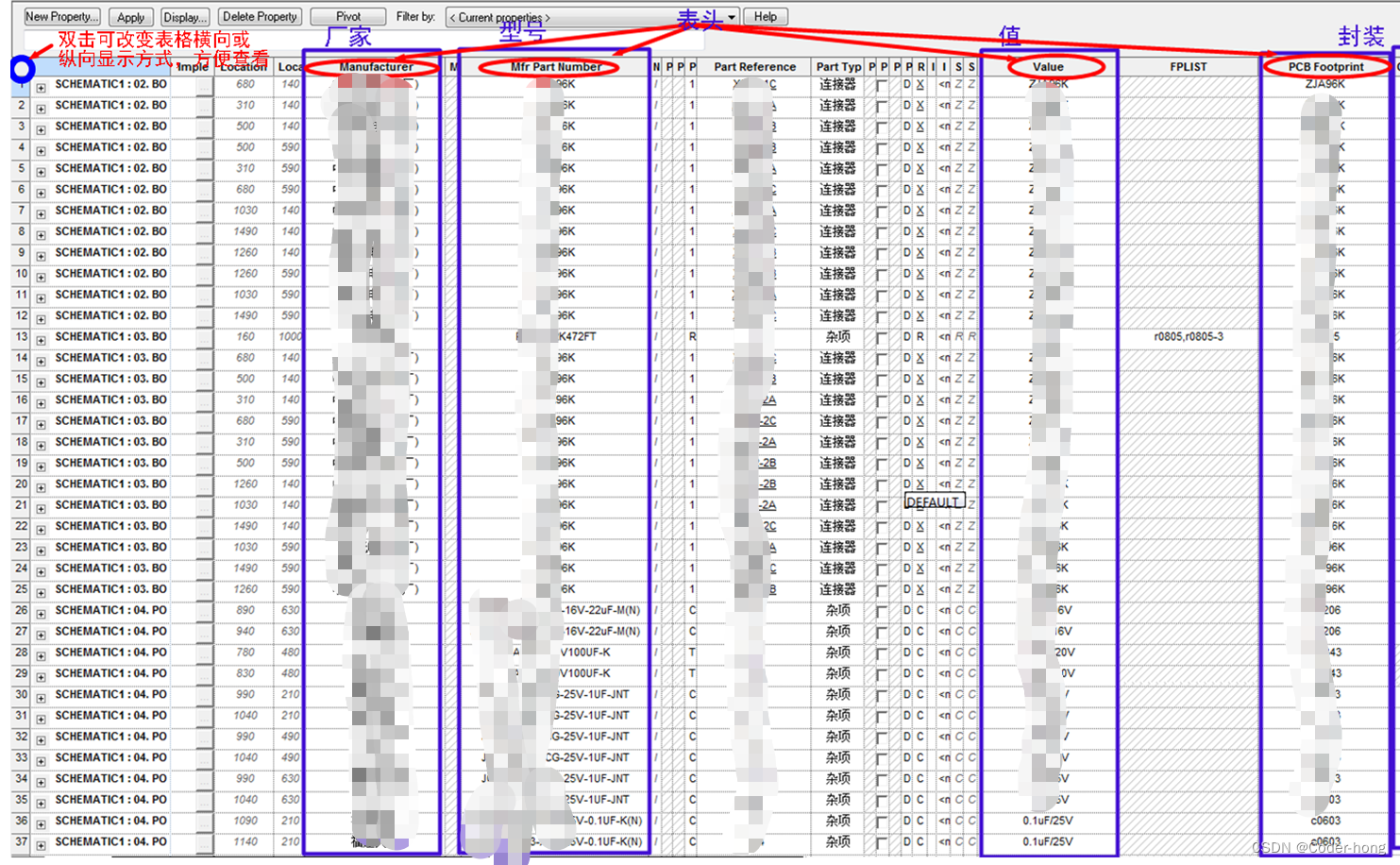

在DSN文件上点右键“Edit Object Properties”,如下图所示主要检查PCB封装,元件型号厂家等信息是否正确。

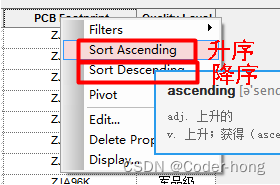

**技巧:**如下图所示每个表头都可点击右键进行升序或降序排列。

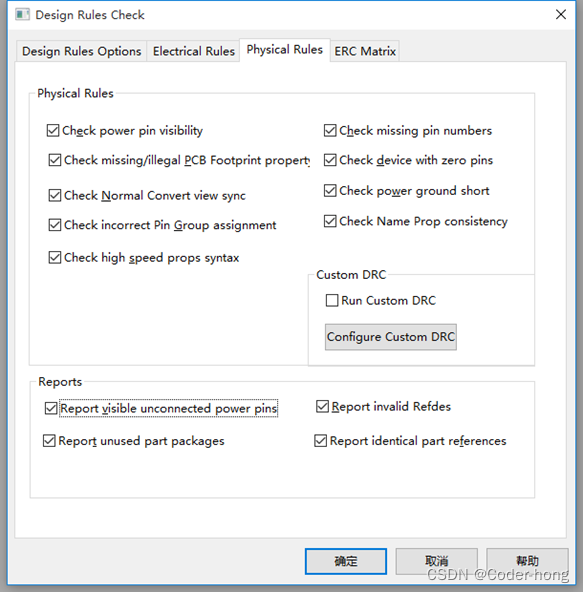

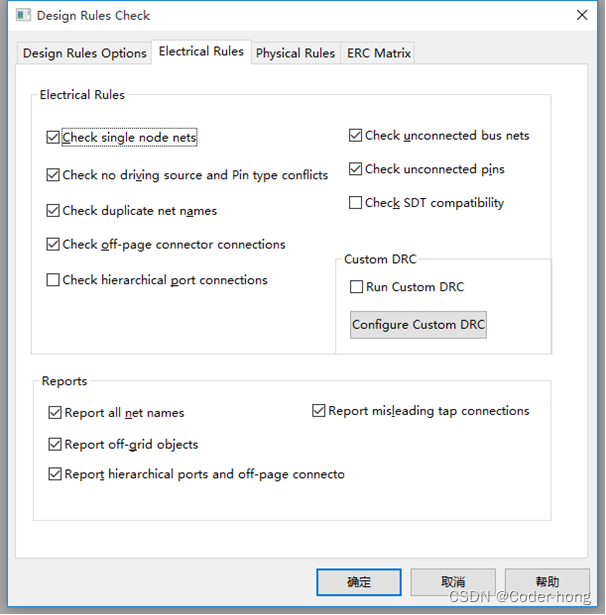

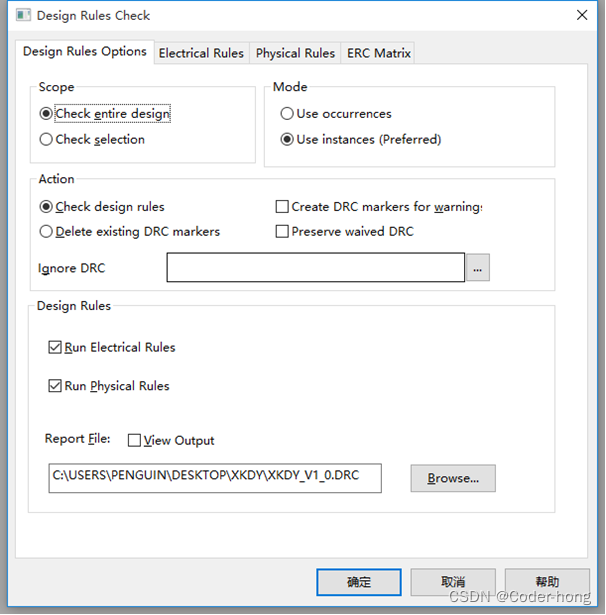

运行DRC

如下图所示配置。完成后需对照日志,逐项进行原理图审查

常见问题:

//网络缺少驱动源:

WARNING(ORCAP-1608): Net has no driving source N17249332//单端网络:

WARNING(ORCAP-1600): Net has fewer than two connections DINRXP1//表示总线BUS没有标名字:

ERROR(ORCAP-1592): Bus has no name and therefore defines no signals. N12821085//表示2个页中有相同的网络名,但没有off-page连接,系统自动重命名,但需设计者确认是否是非电气连接的网络:

WARNING(ORCAP-1611): Two nets in same schematic have the same name, but there is no off-page connector ADC1X_P10 //表示下列元件或网络偏离格点,建议依次进行修改。

Reporting Off-Grid ObjectsC263 - 20. CAMLINK_TX (273.05, 58.42)C259 - 20. CAMLINK_TX (246.13, 58.42)//报告所有page之间互联的Off-page网络,建议拷贝到excel中重新排序,并检查是否有网络名称错误或漏掉的网络编号:

Reporting Off-Page ConnectionsZIO17ZIO28……//报告所有的电源网络,建议逐个确认:

Reporting GlobalsVCC5VVCC_JTAG……//报告所有的网络,建议拷贝到excel中排序,并逐个检查一遍,看是否有错误的网络名:

Reporting Net NamesEX_RS232_TXD2OUT6N17054142……//该错误表示同一个网络上包含2个网络标号,对此需要核实:

QUESTION(ORCAP-1589): Net has two or more aliases - possible short? ADC_SFL Alternate Name: ADC_SDA//封装名称中包含“.”,在导入PCB时会出错,必须修改:

ERROR(ORCAP-36071): Illegal character "Dot(.)" found in "PCB Footprint" property for component instance U20: SCHEMATIC1, 12. VOICE_AD/DA (167.64, 231.14) . /U20: SCHEMATIC1, 12. VOICE_AD/DA (167.64, 231.14)生成网表异常

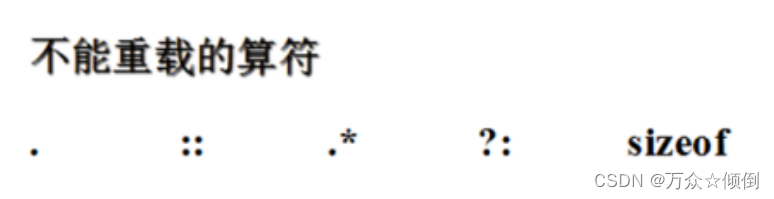

提示冲突值

#5 ERROR(ORCAP-36004): Conflicting values of part name found on different sections of "L4".

Conflicting values: 7448841015_L-5_5X5_5_1.5UH/3.7A & 7448841015_0_L-5_5X5_5_1.5UH/3.7A

Property values of "Device","PCB FootPrint", "Class" and "Value" should be identical on all sections of the part.

#6 ERROR(ORCAP-36018): Aborting Netlisting... Please correct the above errors and retry.检查发现以上“&”符号前后内容存在“_0”的差异,原因是这个器件有2个part组成,其中一个part有问题在原理图中直接编辑更新后导致产生了2个库,处理方法:

- 删除原理图中所有该器件

- 清除原理图设计缓存

- 重新从库中调取元件放置

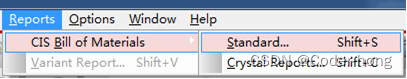

基于CIS库生成bom

如下图所示,选中.DSN工程文件,再点击Report->CIS Bill of Materials->Standard。

生成BOM表,并在EXCEL中打开

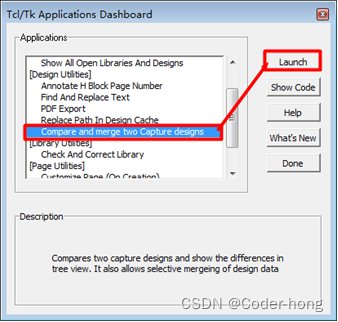

OrCad原理图比较工具

点击Accessories->Cadence Tcl/TK Utilities-> Utilities …后,出现如下窗口

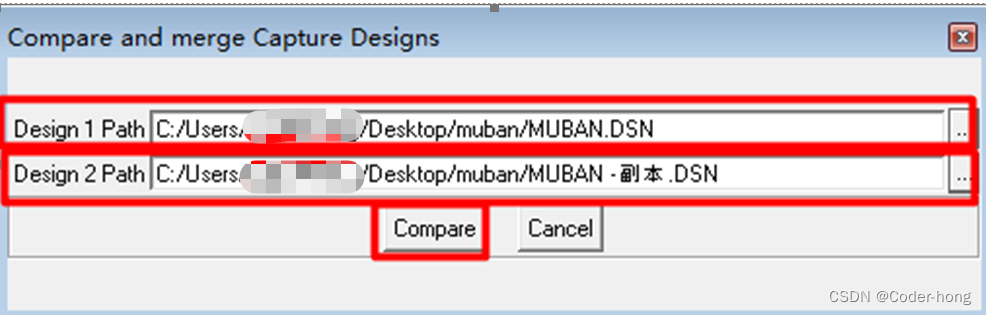

选择Compare and merge two Capture designs->launch显示如下窗口:

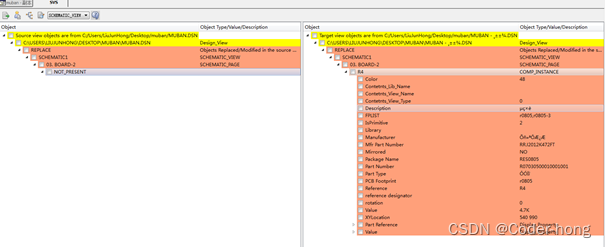

分别选择2个被比较的设计文件,点击比较按钮,比较结果显示在SVS文件中,如下图所示:

上图表示其不同之处是另外一幅图中多了个电阻

Allegro中进行网表比较

准备将要比较的两个PCB设计文件,打开a.brd设计文件,点击tool->Design Compare…打开设计比较窗口,然后再关闭,在该路径会生成a.xml文件。

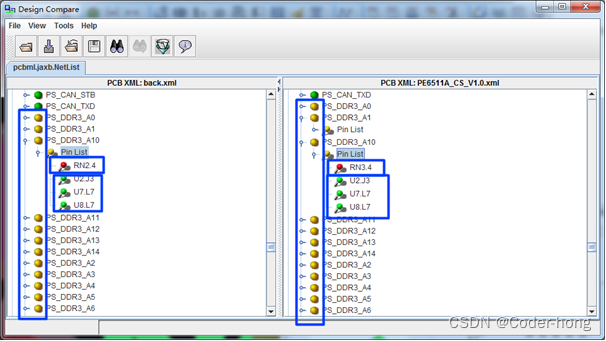

打开b.brd设计文件,点击tool->Design Compare…打开设计比较窗口,点击file->load选择a.xml文件,出现比较窗口如下图所示:

上图中红色表示网表的差异之处,绿色表示完全相同。

Allegro配合进行原理图网络逐个检查

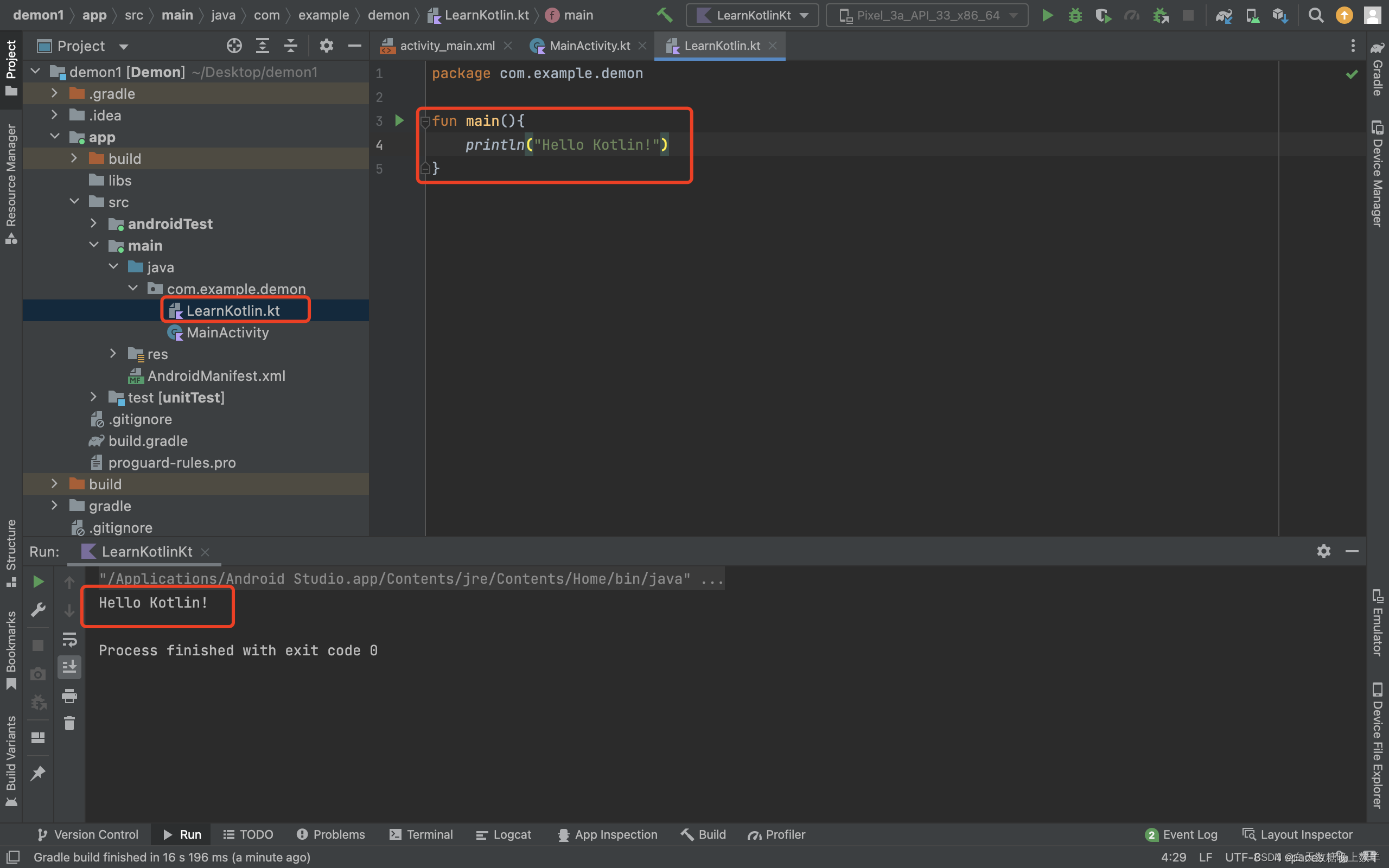

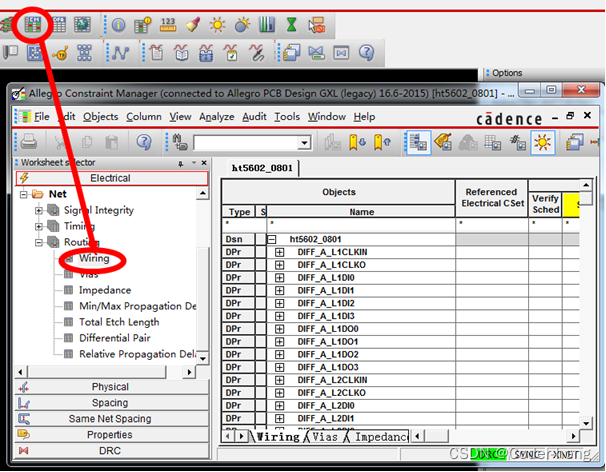

- 创建空白brd设计文件,导入Orcad网表,如下图所示:

- 打开PCB约束管理器

- 选择高亮网络命令:

挨个网络双击,在ORCAD中将高亮所有选择的网络,依次检查每个网络的连线关系是否正确,并注意关键信号是否有遗漏。

检查表

| 序号 | 项目 | 检查内容 | 结论 | 备注 |

|---|---|---|---|---|

| 1 | 系统方案检查检查 | 核实整体各功能模块是否全面,各功能模块选型需与设计方案一致,整板大体布局是否合理,FPGA部分管脚分配是否合理 | ||

| 2 | 供电系统检查 | 检查各芯片需求电源及功耗,画出电源分配系统框图,检查上电时序及各路电源供给是否留有足够的设计余量,检查电源电路配置电阻、检查所有电源网络标号是否正确。 | ||

| 3 | 复位系统检查 | 检查复位电路,复位原理是否满足设计要求,并且留有看门狗复位、掉电预警等电路。 | ||

| 4 | 各元件库检查 | 主要检查各元件的管脚名及管脚号对应关系,非常重要,原理图画完以后经常因为大意出错,检查方法:导出PCB库,在原理图中搜索每个dra文件名,并打开对应数据手册,对照原理图管脚号和对应名称是否一致、对照PCB管脚号与手册是否一致、对照PCB尺寸pin间距与手册是否一致。 | ||

| 5 | 每页原理检查 | 认真阅读DATASHEET,并校验每页原理设计的正确性,以及输入输出管脚电平标准是否匹配。 | ||

| 6 | 网标检查 | 配合Allegro将每个网络挨个点亮一遍,检查是否有漏接或少接的网络。包括电源网络。 | ||

| 7 | 页间连接检查 | 主要检查off-page连接符是否连接正确。 | ||

| 8 | 电源电路检查 | 主要检查电源电路输出电压是否正确,供电电流是否合理。 | ||

| 9 | 加电时序检查 | 检查加电时序是否按照手册要求加电时序进行加电。 | ||

| 10 | 标准化检查 | 图纸标题、页码、名称、代号、原理框图等等 | ||

| 11 | Bom表检查 | 原理图输出bom表,对选型参数和Value/封装进行比对 |