FPGA时钟系列文章总览:

FPGA原理与结构(14)——时钟资源![]() https://ztzhang.blog.csdn.net/article/details/132307564

https://ztzhang.blog.csdn.net/article/details/132307564

一、概述

全局时钟是 FPGA 中的一种专用互连网络,旨在将时钟信号分配到 FPGA 内各种资源的时钟输入处。这种设计考虑了时钟信号在整个芯片上的传播,确保了低偏斜(low skew)、低占空比失真、低功耗以及改进的抖动容忍度。全局时钟网络还支持非常高频率的信号,满足现代高性能电子系统的需求。

1.1 全局时钟网络的设计特点

低偏斜:通过优化时钟信号在 FPGA 内部的传播路径,全局时钟网络能够最小化时钟到达不同资源的时间差异,这对于保证同步操作和提高系统性能至关重要。

低占空比失真:全局时钟网络保证时钟信号的上升沿和下降沿均匀分布,避免时钟信号的占空比发生变化,这有助于维持稳定的时钟周期和提高电路的可靠性。

低功耗:通过减少时钟网络中的电容负载和优化信号传输路径,全局时钟网络设计力求降低功耗,这对于发热控制和提升电池驱动设备的续航能力尤为重要。

改进的抖动容忍度:全局时钟网络通过减少信号抖动,提高时钟信号的稳定性,从而支持高精度的时钟定时需求。

支持高频信号:全局时钟网络被设计来支持非常高频率的信号,满足了现代 FPGA 应用中对快速数据处理和高速通信的需求。

1.2 对全局时钟资源的理解

理解全局时钟的信号路径有助于深入认识 FPGA 中的各种全局时钟资源,包括但不限于 BUFG(全局时钟缓冲器)、PLL(相位锁定环)和 MMCM(混合模式时钟管理器)。这些资源共同工作,提供精确的时钟管理功能,包括时钟生成、分频、选择和门控等。

全局时钟资源的有效利用是 FPGA 设计中的关键环节,它不仅影响电路的性能和稳定性,还涉及到系统的功耗和成本。因此,设计师需要根据应用的具体需求仔细规划时钟网络,以实现最优的性能和资源利用效率。

二、时钟树和网——GCLK

在 Xilinx 的 7 系列 FPGA 架构中,时钟树的设计专注于低偏斜和低功耗运作。这种设计通过断开任何未使用的分支来进一步降低功耗,确保只有需要的时钟信号路径被激活。此外,时钟树还可以用于驱动逻辑资源,例如重置或时钟使能信号,这在需要驱动高扇出/负载网络的应用中尤其有用。

7 系列 FPGA 的一个显著特点是,全局时钟线的引脚访问不限于逻辑资源的时钟引脚。全局时钟线还可以驱动可配置逻辑块(CLB)中的其他引脚,例如控制引脚 SR和 CE(时钟使能)。这提供了额外的灵活性,允许设计师利用高性能的全局时钟网络来实现快速信号连接和管理大负载/扇出需求。

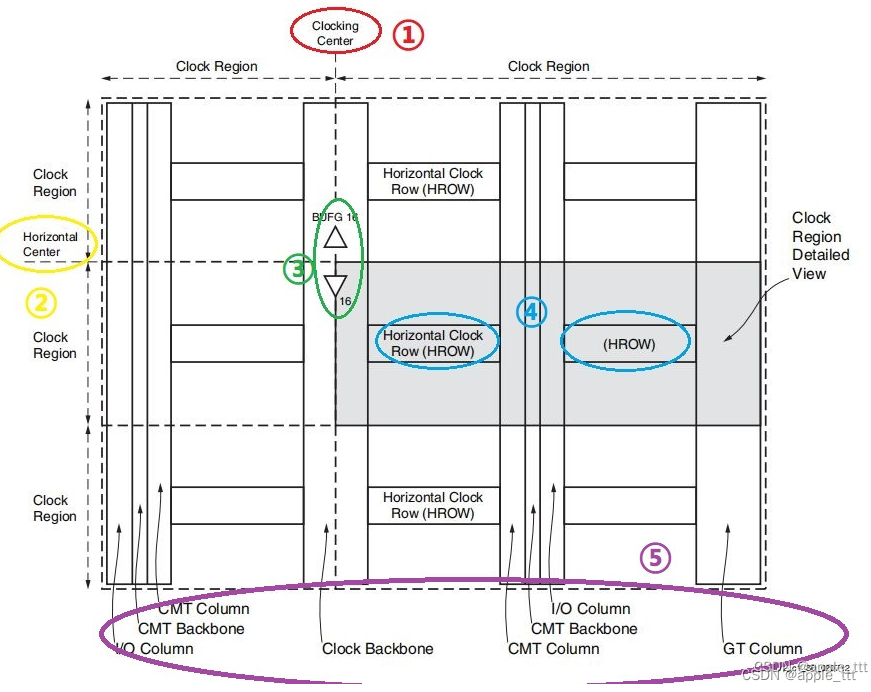

三、时钟区域

7系列 FPGA 设备通过使用时钟区域改进了时钟分配机制。时钟区域的设计使得时钟信号的分配更为高效和灵活,有助于提高整体系统的性能和稳定性。以下是7系列设备时钟分配机制的关键特点:

3.1 时钟区域与全局时钟域

3.1.1 时钟区域(Clock Regions)

时钟区域是 FPGA 内部用于划分和管理时钟信号的物理区域。在 Xilinx 7 系列 FPGA 中,一个时钟区域定义为包含一定数量的可配置逻辑块(CLBs)的区域,通常跨越 FPGA 设备的一半宽度,并向上和向下延伸多个(25个) CLB 行。时钟区域的主要目的是优化和控制时钟信号在特定区域内的分配,以减少时钟偏斜和延迟,提高设计的稳定性和性能。

时钟区域的定义:每个时钟区域可以拥有多达12个全局时钟域。这些全局时钟域能够被任意组合中的32个全局时钟缓冲器驱动,这些缓冲器在单片设备或超大规模集成(SLR,Super Logic Region)中可用。

时钟区域的尺寸:时钟区域的尺寸固定为50个CLB块高(50个I/O块),并跨越芯片的左侧或右侧。这种设计确保了时钟信号可以有效地覆盖特定区域,同时减少信号传播的延迟和偏斜。

3.1.2 全局时钟域(Global Clock Domains)

全局时钟域指的是 FPGA 设计中被全局时钟信号覆盖的逻辑部分。全局时钟信号通常由全局时钟缓冲器(如 BUFG)分发,旨在提供低偏斜、高稳定性的时钟源给 FPGA 设计中的各个模块。一个全局时钟域可以跨越多个时钟区域,支持设计中不同功能模块的同步运作。

3.2 设备分割与时钟主干

时钟主干:7系列设备中的时钟背骨将设备分割为左侧或右侧。重要的是,这个主干并不位于芯片的中心,这种设计有助于优化时钟信号在芯片上的分布和管理。

时钟区域数量:通过固定时钟区域的尺寸,更大的7系列设备可以拥有更多的时钟区域。7系列 FPGA 提供1到24个时钟区域,不同型号的设备提供的时钟区域数量不同,以满足不同规模设计的需求。

总之,7系列 FPGA 设备的时钟区域机制为时钟信号的高效分配和管理提供了强大的支持,这对于满足现代高性能电子系统的需求至关重要。通过充分利用这一机制,设计师可以优化他们的时钟网络设计,实现更高的系统性能和稳定性。

四、全局时钟缓冲器

在7系列的FPGA中,有着多达32个全局时钟缓冲器(BUFG)。32个BUFG被划分成两组,每组16个BUFG,分别位于设备的顶部和底部。

设备上半部分的 CMT 只能驱动上半部的 BUFG,而下半部分的 CMT 只能驱动下半部的 BUFG。同样,只有同一半设备内的 BUFG 才能作为反馈信号提供给同一半设备内的 CMT。这种设计确保了时钟网络在物理布局上的优化,有助于降低时钟传播延迟和偏斜。

一个CC(Clock-Capable)input 可以直接连接到同一半设备中(上下划分)的任何全局时钟缓冲器。每对差分时钟引脚都可以连接到PCB上的差分或单端时钟。Xilinx 7系列 FPGA 的CC input 通过存在于时钟主干的垂直时钟网络间接驱动全局时钟缓冲器(BUFG)。任何直接连接到BUFG的资源(例如,GTX收发器)都有顶部/底部的限制。例如,顶部的每个MMCM只能驱动位于设备顶部的16个BUFG。同样,底部的MMCM驱动底部的16个BUFG。

在7系列设备中,所有全局时钟缓冲器可以驱动所有时钟区域。然而,在单个时钟区域内,只能驱动12种不同的时钟(也就是一个时钟区域最多包含12个全局时钟域)。时钟区域(包括50个CLBs)是时钟树的一部分,其中25行CLB在上,25行CLB在下,横跨设备的一半。

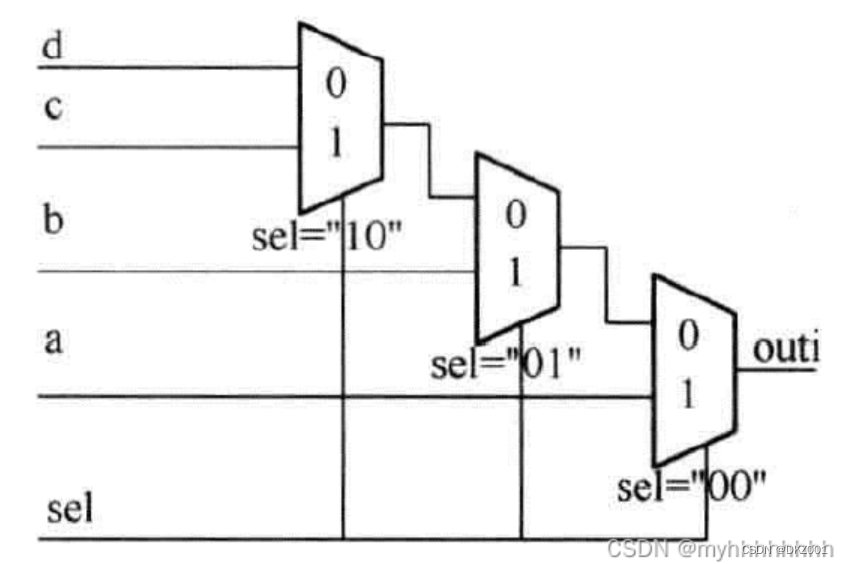

时钟缓冲器被设计为可以配置为同步或异步无抖动的2:1多路复用器,具有两个时钟输入。存在专用路径(路由资源)用于BUFG级联,以允许选择两个以上的时钟输入。

在 Xilinx 7 系列 FPGA 的时钟架构中,BUFGCTRL 多路复用器及其所有衍生形式能够在设备上半部和下半部各自的16个时钟缓冲器组内相邻的时钟缓冲器之间进行级联,有效地在上半部和下半部分别创建一个包含16个 BUFGMUX(BUFGCTRL 多路复用器)的环形网络。这种设计极大地增加了时钟网络的灵活性和扩展性,允许设计师构建复杂的时钟选择和分配方案。

BUFGCTRL 多路复用器的级联:

级联功能:通过将一个 BUFGCTRL 的输出连接到另一个 BUFGCTRL 的输入,可以构建一个连续的时钟路径,这允许从多个时钟源中选择时钟信号,同时最小化时钟传播延迟和偏斜。

环形网络:在设备的上半部和下半部,这些 BUFGCTRL 多路复用器可以形成两个独立的环形网络,每个网络包含16个 BUFGMUX。这种环形结构提供了强大的时钟选择和分配能力,同时保持了低功耗和高效率。

应用:这种级联和环形网络的设计非常适合于需要动态选择不同时钟源的应用,例如在不同操作模式之间切换或实现时钟门控逻辑。

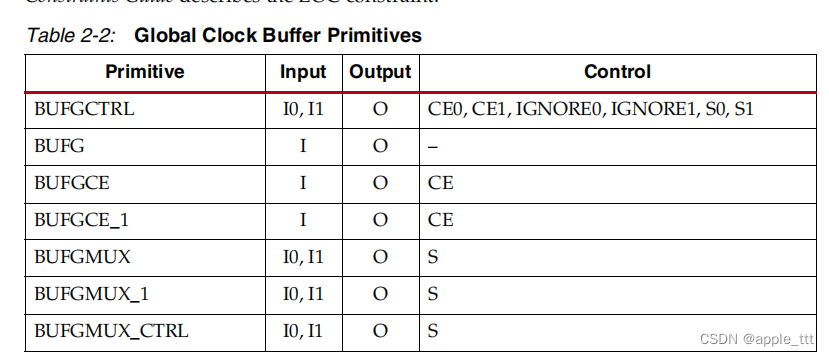

五、全局时钟缓冲器原语

原语总表如下所示:

在 Xilinx FPGA 设计中,上面所有的时钟原语(primitives)都是基于 BUFGCTRL 的软件预设衍生而来。BUFGCTRL 是一个非常灵活的全局时钟缓冲器控制原语,提供了广泛的功能,包括时钟选择、时钟门控以及时钟分频等。通过利用这些软件预设,设计师可以实现复杂的时钟管理策略,优化时钟网络的性能和资源利用率。

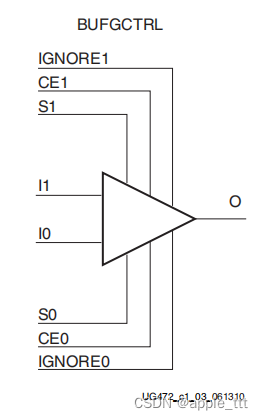

5.1 BUFGCTRL

BUFGCTRL 原语能够在两个异步时钟之间进行切换,所有其他的全局时钟缓冲区原语都来自于BUFGCTRL的某些配置。

BUFGCTRL 是 Xilinx FPGA 中一个非常强大且灵活的全局时钟缓冲器控制原语,它允许设计师基于多种控制信号来选择和管理时钟信号。具有四条选择线(S0, S1, CE0, 和 CE1)以及两条额外的控制线(IGNORE0 和 IGNORE1),BUFGCTRL 提供了对两个输入 I0 和 I1 高度的控制能力。

5.1.1 控制线的作用

-

S0 和 S1:这两条线用于选择输入(I0 或 I1)作为 BUFGCTRL 的输出。通过不同的 S0 和 S1 组合,设计师可以实现时钟输入的动态选择。

-

CE0 和 CE1:时钟使能(Clock Enable)线,用于控制是否使能对应的输入 I0 和 I1。当 CE 线被置为有效(通常是高电平)时,对应的时钟输入被允许通过到输出;当 CE 线为无效时,对应的输入被禁用。

-

IGNORE0 和 IGNORE1:这两条控制线提供了对 BUFGCTRL 行为的额外控制。通过设置 IGNORE 线,设计师可以指示 BUFGCTRL 忽略对应的 CE 线的状态,这在某些特定的时钟管理策略中非常有用。

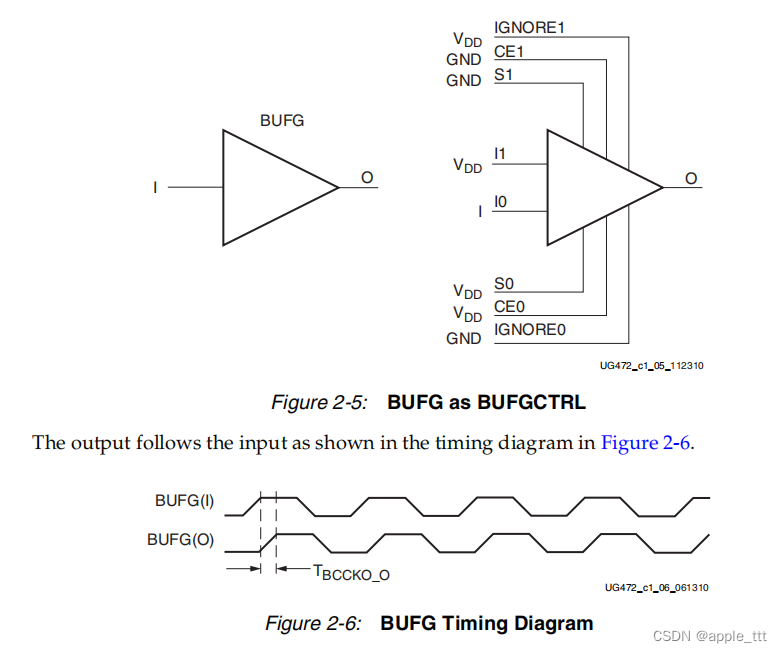

5.2 BUFG

BUFG 是 Xilinx FPGA 中的一种基本时钟缓冲器原语,它具有一个时钟输入和一个时钟输出。这个原语基于 BUFGCTRL 设计,但是其一些引脚被固定连接到逻辑高(High)或逻辑低(Low),简化了其使用方式,使其成为实现单一时钟源分配的理想选择。通过将某些控制信号固定为高或低,BUFG 能够以更简单的配置满足大多数常见的时钟缓冲需求。

5.3 BUFGCE and BUFGCE_1

BUFGCE 是一种在 Xilinx FPGA 设计中用于时钟管理的原语,与 BUFG 类似,但它增加了一个时钟使能(CE)线。这使得设计师能够根据需要动态地使能或禁用时钟信号,提供了对时钟信号更精细的控制,从而优化系统性能和功耗。

BUFGCE_1 是一种特殊的全局时钟缓冲器,类似于 BUFGCE,但其在时钟使能(CE)控制和时钟信号切换条件方面有所不同。这种差异主要体现在对 CE 输入信号的响应以及时钟信号的输出行为上。

5.3.1 BUFGCE

- 通用行为:当 CE 输入为高(逻辑高)时,BUFGCE 允许时钟信号从输入传递到输出。当 CE 输入为低(逻辑低)时,时钟信号被阻塞,不会传递到输出。

- 输出状态:在 CE 为低时,即时钟信号被禁用时,输出的具体状态(高或低)取决于时钟信号被禁用时的最后状态。

5.3.2 BUFGCE_1

- 特殊的切换条件:BUFGCE_1 的区别在于,如果 CE 输入在即将到来的下降时钟边沿之前为低,则接下来的时钟脉冲不会通过时钟缓冲器,输出保持高。

- CE 输入的变化:在即将到来的时钟低脉冲期间,CE 的任何电平变化都不会产生效果,直到时钟信号向高跳变。这意味着,即使 CE 在时钟低脉冲期间变高,输出也会保持高状态,直到下一个时钟高脉冲的开始。

- 时钟禁用时的输出:当时钟被禁用时,输出保持高状态。然而,如果在禁用时钟的过程中,BUFGCE_1 会完成时钟的低脉冲,确保时钟信号的完整性。

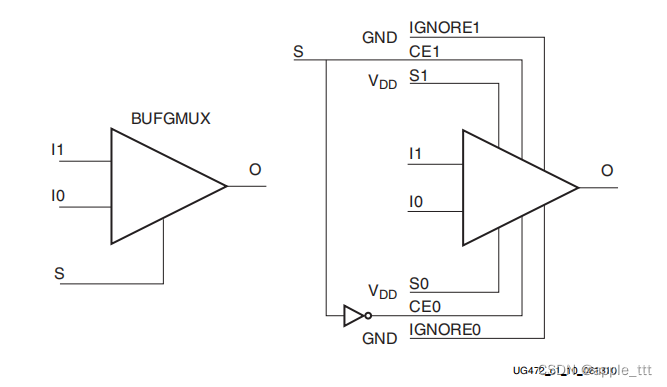

5.4 BUFGMUX and BUFGMUX_1

BUFGMUX 是 Xilinx FPGA 中的一种时钟缓冲器原语,它具备两个时钟输入、一个时钟输出以及一个选择线。这种原语是基于 BUFGCTRL 设计的,通过将某些引脚固定连接到逻辑高(High)或逻辑低(Low),实现了更专用的功能。BUFGMUX 允许设计师根据选择线的状态动态选择两个时钟输入中的一个来传递到输出,从而为设计提供了更大的灵活性和时钟管理能力。

在 Xilinx FPGA 设计中,BUFGMUX 和 BUFGMUX_1 都是用于时钟信号选择的全局时钟缓冲器原语,但它们在时钟选择行为和逻辑上存在细微差异。这些差异影响了它们在特定设计场景中的应用方式。

5.4.1 BUFGMUX

- 基本功能:BUFGMUX 允许设计师根据选择信号(S)的状态动态选择两个输入时钟(I0 和 I1)中的一个作为输出。

- 选择逻辑:通常,当选择信号 S 为高(逻辑高)时,I1 被选为输出;当 S 为低(逻辑低)时,I0 被选为输出。

5.4.2 BUFGMUX_1

- 特殊行为:BUFGMUX_1 与 BUFGMUX 类似,提供两个时钟输入和一个选择线,但在具体的时钟选择和切换逻辑上可能有所不同。具体差异可能涉及到对选择信号变化的响应时间、时钟切换的同步/异步行为等方面,依据不同的 FPGA 版本和设计需求可能有所调整。

- 应用场景:BUFGMUX_1 的这些特殊行为使其在需要对时钟切换时机或行为有特殊要求的应用中更为适用。

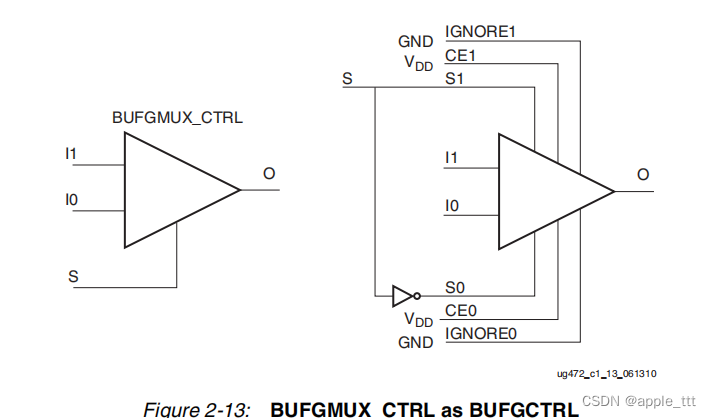

5.5 BUFGMUX_CTRL

BUFGMUX_CTRL是一个更新的时钟缓冲器原语,它取代了旧的BUFGMUX_VIRTEX4 原语。这表明 Xilinx 在其 FPGA 设计工具和库中进行了更新,以提供更加灵活和强大的时钟管理能力。 BUFGMUX_CTRL继承了BUFGMUX的基本功能,并在此基础上增加了更多控制选项,使其更加符合现代 FPGA 设计的需求。

BUFGMUX_CTRL 的特性如下:

- 两个时钟输入:提供两个时钟输入端口(I0 和 I1),允许连接两个独立的时钟源。

- 一个时钟输出:无论选择哪个输入,

BUFGMUX_CTRL都将所选的时钟信号输出到其单一的输出端口。- 选择线:通过一个选择线(S),设计师可以控制是将 I0 或 I1 的时钟信号输出。这提供了动态选择时钟信号的能力,适用于需要在运行时切换不同操作模式的设计。

- 基于 BUFGCTRL:

BUFGMUX_CTRL原语是基于BUFGCTRL实现的,通过将BUFGCTRL的某些引脚固定连接到逻辑高(High)或逻辑低(Low),实现了时钟选择功能。

![[机缘参悟-162/管理者与领导者-151] :受害者心态与受害者思维模式,如何克服受害者思维模式,管理者如何管理这种思维模式的人?](https://img-blog.csdnimg.cn/direct/a7c5ab20263b43aca59b02312b89847f.png)