Q:介绍完计数器分频电路概念原理之后,本期我们设计实现四分频计数器分频电路。

A:使用DE2-115开发板的KEY[1]作为时钟i_clk输入,KEY[0]作为清零复位i_rst输入,LEDR[0]显示分频后的时钟o_clk输出值,LEDR[3:1]显示计数值输出。

4分频计数器的Verilog代码:

在顶层.v文件中例化分频器:

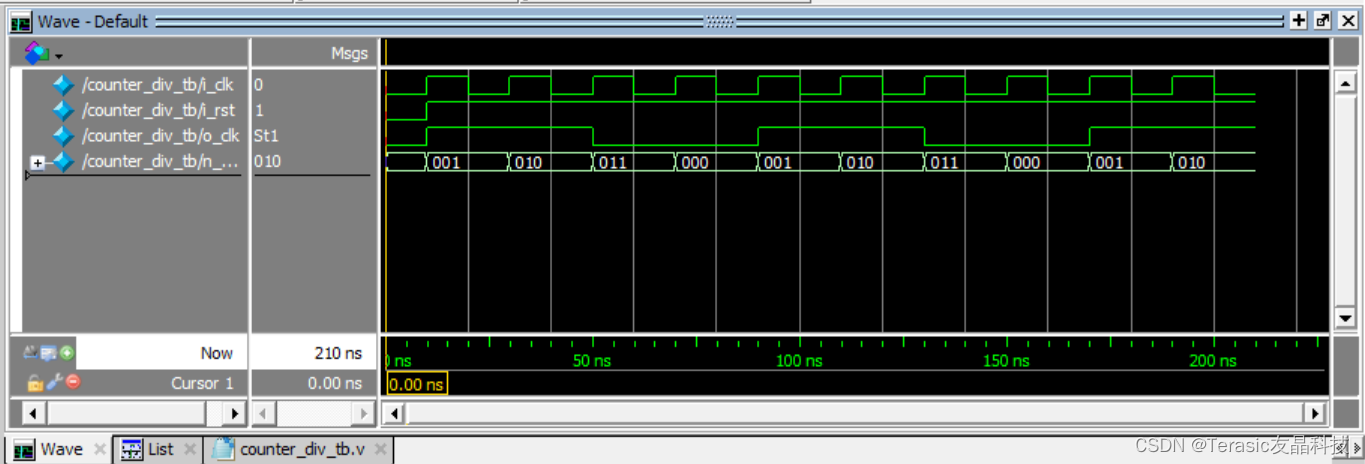

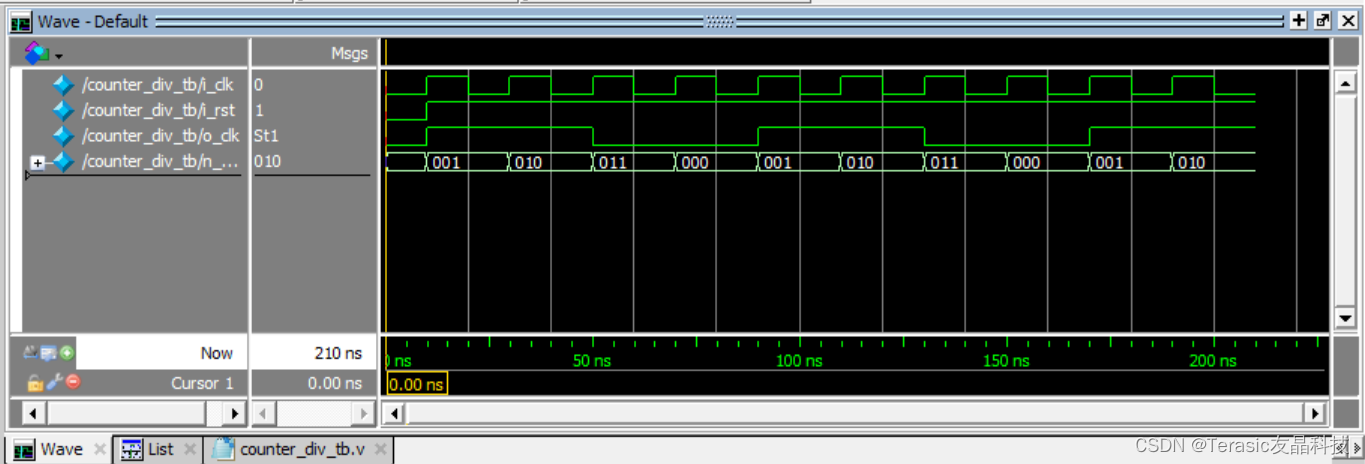

Modelsim仿真结果:输出时钟o_clk波形频率为输入时钟频率的1/4,且占空比是50%。

Q:介绍完计数器分频电路概念原理之后,本期我们设计实现四分频计数器分频电路。

A:使用DE2-115开发板的KEY[1]作为时钟i_clk输入,KEY[0]作为清零复位i_rst输入,LEDR[0]显示分频后的时钟o_clk输出值,LEDR[3:1]显示计数值输出。

4分频计数器的Verilog代码:

在顶层.v文件中例化分频器:

Modelsim仿真结果:输出时钟o_clk波形频率为输入时钟频率的1/4,且占空比是50%。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.luyixian.cn/news_show_1046130.aspx

如若内容造成侵权/违法违规/事实不符,请联系dt猫网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!