期中考试【Verilog】

- 前言

- 推荐

- 期中考试

- 一. 单选题(共10题)

- 二. 填空题(共5题)

- 三. 简答题(共3题)

- 四. 其它(共4题)

- 最后

前言

编写于2022/11/30 13:30

以下内容源自Verilog期中试题

仅供学习交流使用

考试时间 8:40~10:00

首次做:不翻书 9:20左右做完

再次检查:翻书 9:50左右做完

题目难度:不是很难,尽量不翻书

推荐

第四章 数字逻辑电路设计方法【Verilog】

期中考试

题量:22满分:100

作答时间: 11-30 08:41至11-30 10:00

一. 单选题(共10题)

1.(单选题)门级建模的类型有( )

A. or和AND

B. OR和and

C. and和or

D. A、B、C都正确

我的答案: C 必须是小写

正确答案: C

2.(单选题)

VerilogHDL使用的逻辑是( )

A. 二值逻辑

B. 四值逻辑

C. 三值逻辑

D. 八种强度

我的答案: B 0、1、x、z

正确答案: B

3.(单选题)具有多个输出端口的门是( )

A. and

B. or

C. nor

D. not

我的答案: D 基本门电路这个not很特殊,多输出门 另外还有缓存器buf

正确答案: D

4.(单选题)reg[15:0] mem[127:0] 正确的赋值是( )

A. mem[5]=16’ d0;

B. mem=16’ d0;

C. mem[15][127]=1’ b1;

D. mem[5][3:0]=16’ d1

我的答案: A 位宽 个数

正确答案: A

5.(单选题)

下列标识符中那个是合法的( )

A. \din

B. ALWAYS

C. _out*

D. $abc

我的答案: D 我就这个没有检查,以为自己肯定对

正确答案: B 结果,就这个错了

合法标识符只能有数字、字母、下划线、美元符组成

区分大小写

第一个字符只能是字母或下划线

6.(单选题)在verilog语言中,a=4’b1011,那么 &a=( )

A. 4’b1011

B. 4’b1111

C. 1’b1

D. 1’b0

我的答案: D 归约与

正确答案: D

7 (单选题)在verilog语言中整型数据与( )位寄存器数据在实际意义上是相同的。

A. 8

B. 16

C. 32

D. 64

我的答案: C 整型数据4个字节

正确答案: C

8.(单选题)assign连续赋值语句主要用于对( )类型变量赋值。

A. wire √

B. reg

C. integer

D. time

我的答案: A

正确答案: A

9.(单选题)

verilog语言内部已使用的词称为关键字或保留字,( )不是关键字。

A. output

B. tri

C. Module √

D. begin

我的答案: C

正确答案: C

10.(单选题)

过程赋值语句,多用于对( )类型语句赋值。

A. reg √

B. wire

C. net

D. integer

我的答案: A

正确答案: A

二. 填空题(共5题)

11.(填空题)

verilog语言规定的两种主要物理数据类型分别是____________和_____________,程序模块中输入输出信号的缺省类型为___________________。

我的答案:

(1) 连线型

(2) 寄存器型

(3) wire

正确答案:

(1) 连线类型;寄存器类型

(2) 寄存器类型;连线类型

(3) wire

12.(填空题)

块语句有两种,一种是begin-end语句,通常用来标志________________执行的语句;另一种是fork-join语句,通常用来标志________________执行的语句。

我的答案:

(1) 串行

(2) 并行

正确答案:

(1) 顺序

(2) 并行

13.(填空题)

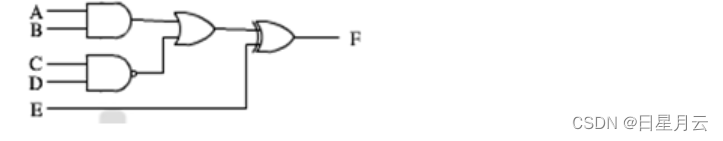

写出表达式以实现对应电路的逻辑功能

assign F=__________________________________。

我的答案:

(1) (A&B)|(C与非D)异或E 我的想法是写成(AB+(–CD))⊕E ,数字电路的表达式有点符号打不出来,用了汉字代替

正确答案:

(1) ((A&B)|(~ (C&D)))^ E;(A&B|(~ (C&D)))^E

- (填空题)

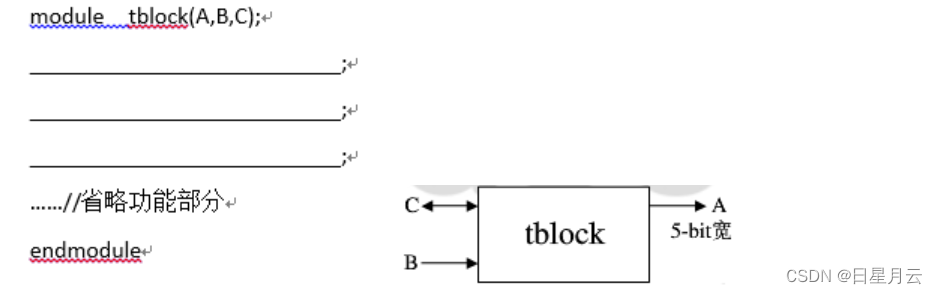

根据图中输入输出关系将verilog模块定义补充完整,其中信号A为5比特宽度,其余信号为1比特宽度。

我的答案:

(1) output[4:0] A

(2) input B

(3) inout C

正确答案:

(1) input B;

(2) inout C ;

(3) output [4:0] A;

15.(填空题)

1、 假设某4比特位宽的变量a的值为4’b1010,计算下列运算表达式的结果:

&a=_______________________;

{3{a}}=____________________;

!a=_______________________。

我的答案:

(1) 1’b0 归约与

(2) 12’b101010101010 复制

(3) 0 逻辑非

正确答案:

(1) 0;1’b0

(2) 12’b101010101010

(3) 0;1’b0

三. 简答题(共3题)

16.(简答题)请解释下列名词:HDL,EDA,FPGA,IP,RTL。

看书

HDL:是一种高级程序设计语言,通过对数字电路和系统的语言描述,可以对数字集成电路进行设计和验证

EDA:一些公司提供功能强大的电子设计自动化工具

FPGA:现场可编程门阵列

IP核:具有知识产权核的集成电路芯核的总称

RTL:数字电路设计和代码编码阶段

17.(简答题)always语句和initial语句的关键区别是什么?能否相互嵌套?

initial:在时刻0开始,只能执行一次

always:在触发条件下,便可执行

不能相互嵌套

18.(简答题)

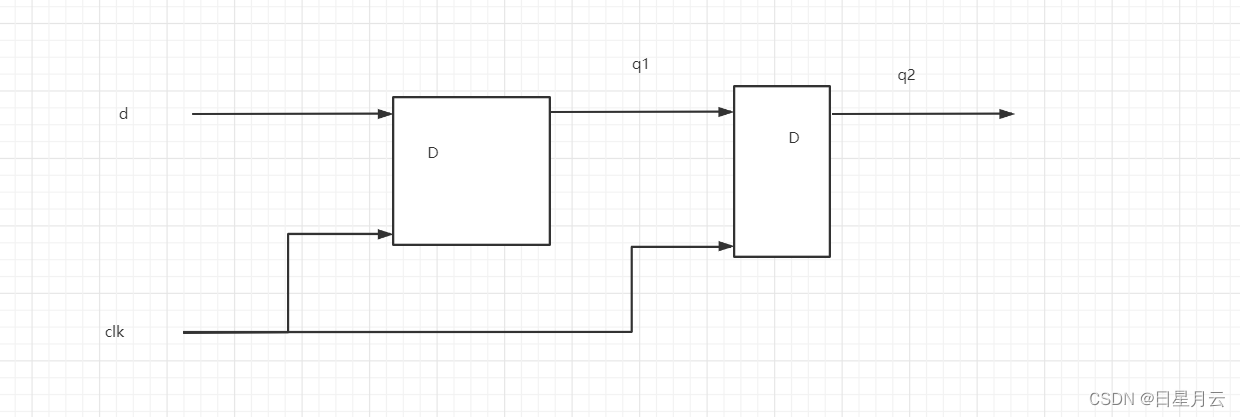

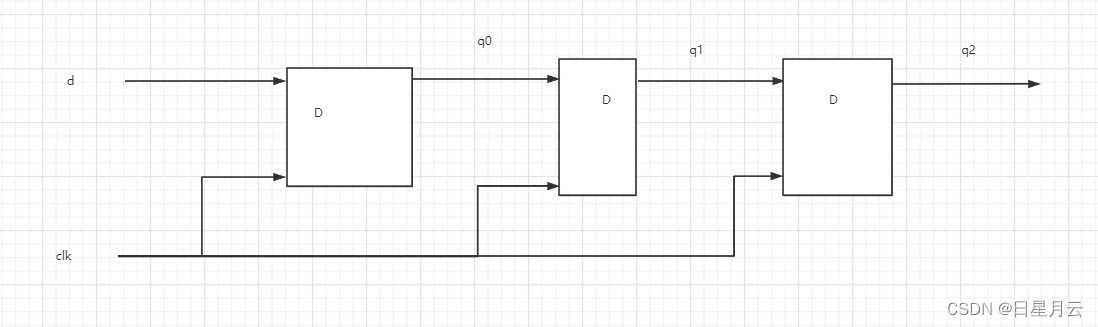

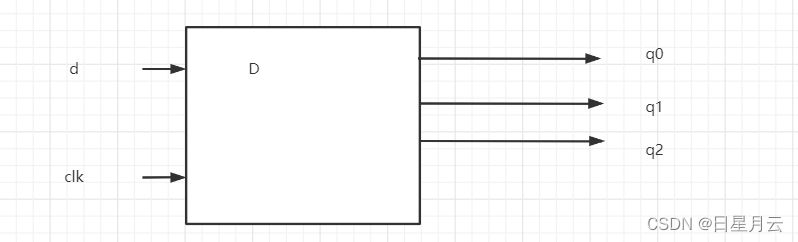

分别画出下面两个程序综合出的电路图(其中d为输入)。

阻塞赋值=和非阻塞赋值<=的区别

① input d,clk;output q0,q1,q2; reg q0,q1,q2;always@(posedge clk)beginq0<=d;q1<= q0;q2<= q1;end② input d,clk;output q0,q1,q2; reg q0,q1,q2; always@(posedge clk)beginq0= d;q1= q0;q2= q1;end

我的答案:

我少画了一个D触发器输出q0

测试

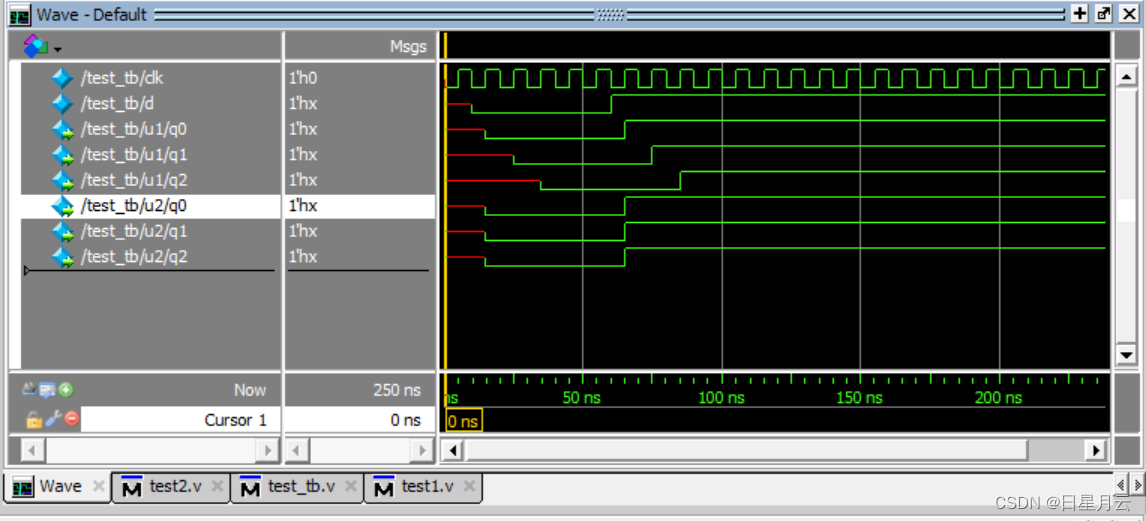

module test1(q0,q1,q2,clk,d);input d,clk;output q0,q1,q2; reg q0,q1,q2;always@(posedge clk)beginq0<=d;q1<= q0;q2<= q1;end

endmodule

module test2(q0,q1,q2,clk,d);input d,clk;output q0,q1,q2; reg q0,q1,q2;always@(posedge clk)beginq0 = d;q1 = q0;q2 = q1;end

endmodule

module test_tb;reg d,clk;wire q0,q1,q2; test1 u1(q0,q1,q2,clk,d);test2 u2(q0,q1,q2,clk,d);always #5 clk = ~clk;initialbeginclk=0;#10 d=0;#50 d=1; end

endmodule

四. 其它(共4题)

19.(其它)

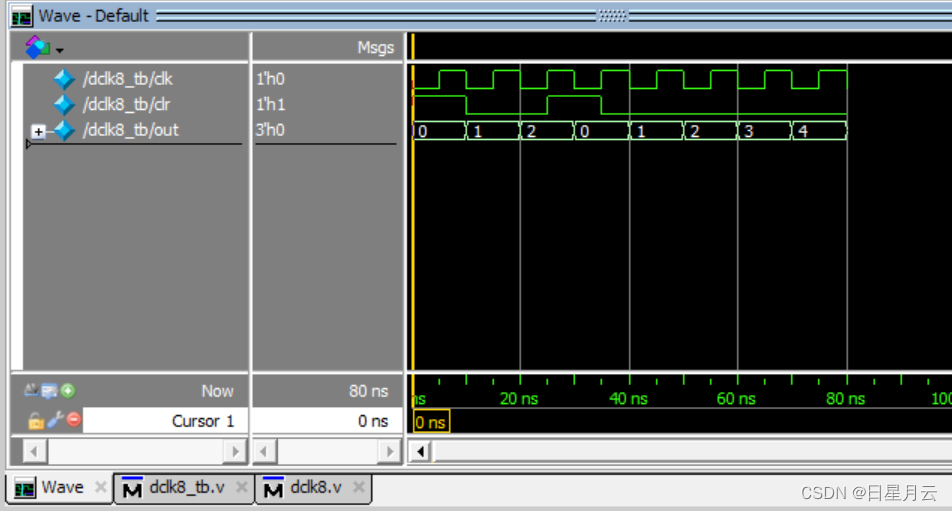

设计一个带复位端且对输入时钟clk进行八分频的电路模块。并设计相应的测试电路。

设计要求:复位信号为同步、高电平有效,时钟的下降沿触发。

module dclk8(out, clk, clr); output [2:0] out; input clk,clr; reg [3:0] out;//少了always @ (negedge clk) //negedgeif (clr) out<=3'b000; else if (out==3'b111) out<=3'b000; else out<=out+1;

endmodule

module dclk8_tb; wire[2:0] out; reg clk,clr; dclk8 u1(out, clk, clr); always #5 clk = ~clk;initialbeginclk=0;clr=1;#10 clr=0;#15 clr=1;#10 clr=0;//应该再补个clr=0 end

endmodule仿真结果:如下

只有计数器,不能实现分频

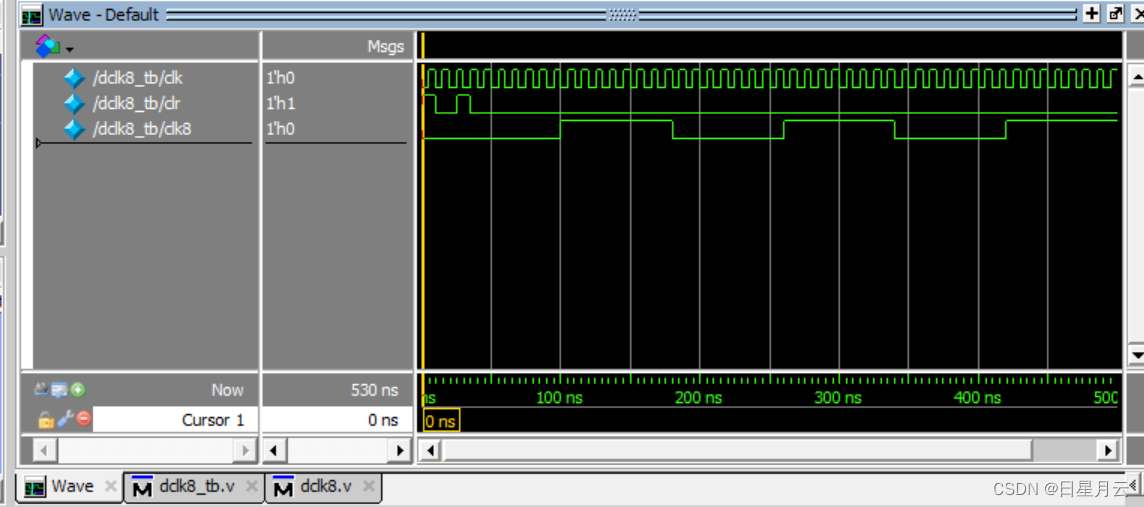

修改

//设计一个带复位端且对输入时钟clk进行八分频的电路模块。并设计相应的测试电路。

//设计要求:复位信号为同步、高电平有效,时钟的下降沿触发。

/*

module dclk8(out, clk, clr); output[3:0] out; input clk,clr; reg [3:0] out;always @ (negedge clk) //negedgeif (clr) out<=3'b000; else if (out==3'b111) out<=3'b000; else out<=out+1; endmodule

*/module dclk8(clk8, clk, clr); output clk8; input clk,clr; reg clk8;reg [3:0] out;always @ (negedge clk) //negedgeif (clr) out<=3'b000; else if (out==3'b111) out<=3'b000; else out<=out+1; always @ (out) if (clr) clk8<=0; else if (out==3'b111) clk8=~clk8;endmodule

/*

module dclk8_tb; wire[2:0] out; reg clk,clr; dclk8 u1(out, clk, clr); always #5 clk = ~clk;initialbeginclk=0;clr=1;#10 clr=0;#15 clr=1;#10 clr=0;//应该再补个clr=0 end

endmodule

*/module dclk8_tb; wire clk8; reg clk,clr; dclk8 u1(clk8, clk, clr); always #5 clk = ~clk;initialbeginclk=0;clr=1;#10 clr=0;#15 clr=1;#10 clr=0;//应该再补个clr=0 end

endmodule

20.(其它)

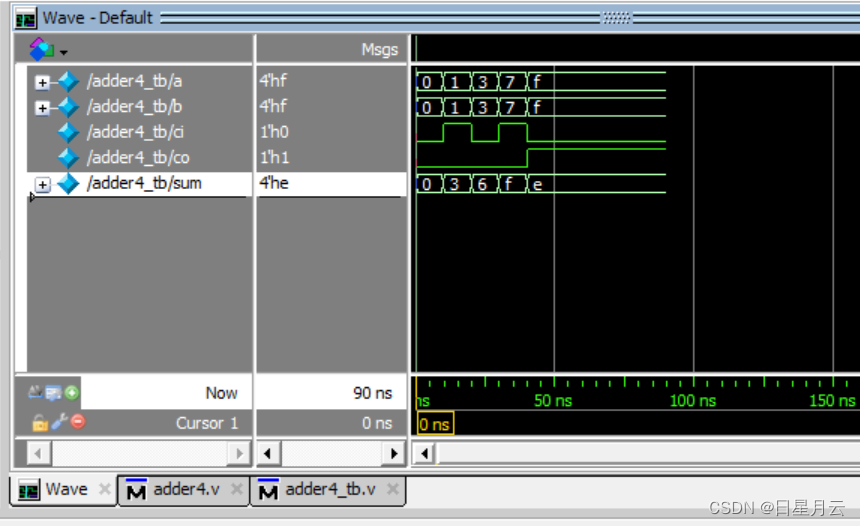

试用Verilog HdL描述一个4位的全加器,并编写测试代码。(端口A、B为加数,CI为进位输入,SUM为和,CO为进位输出。)

module adder4(sum, co, a, b, ci);output[3:0] sum;output co;input[3:0] a, b;input ci;assign {co,sum}=a+b+ci;

endmodule

module adder4_tb;wire[3:0] sum;wire co;reg[3:0] a,b;reg ci;adder4 u4(sum, co, a, b, ci);//我把实例化忘了initialbegina=4'b0000;b=4'b0000;ci=0;#10 a=4'b0001;b=4'b0001;ci=1;#10 a=4'b0011;b=4'b0011;ci=0;#10 a=4'b0111;b=4'b0111;ci=1; #10 a=4'b1111;b=4'b1111;ci=0; end

endmodule

21.(其它)

设计一奇偶校验位生成电路,输入八位总线信号bus,输出奇校验位odd,偶校验位even。并设计相应的测试电路。

module checker8 (odd,even,bus); output odd,even;input [7:0] bus; assign even=^bus; assign odd=~even;

endmodule

module checker8_tb; wire odd,even;reg [7:0] bus; checker8 u8(odd,even,bus);//我把实例化忘了initial beginbus=8'b00000000;#10 bus=8'b00000001;#10 bus=8'b10000000;#10 bus=8'b11111111;end

endmodule

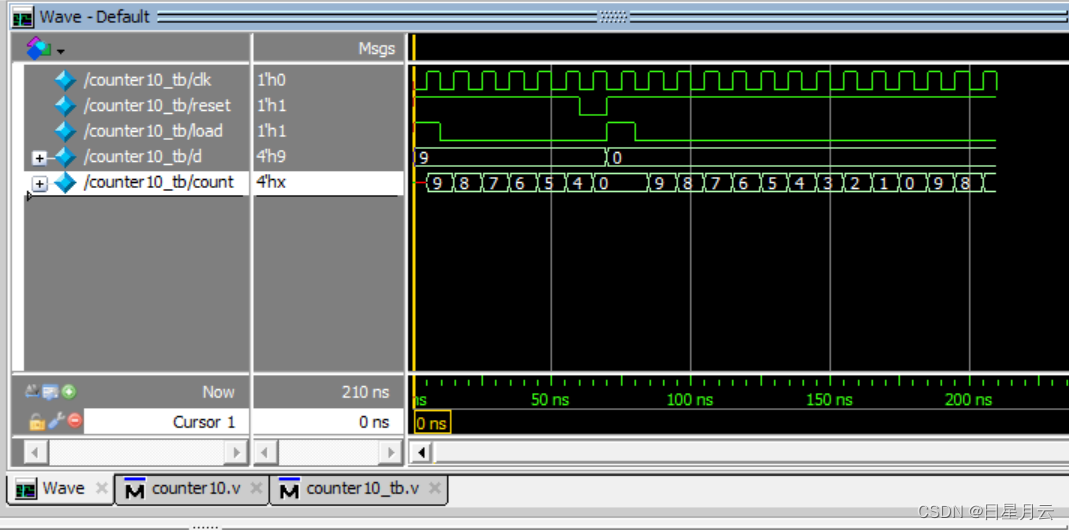

22.(其它)

请用Verilog Hdl设计一个十进制的同步减法计数器,要求具有复位和置数功能,并编写测试代码。

module counter10(count, clk, reset,load,d); output [3:0] count; input clk,reset,load; input [3:0] d; reg [3:0] count;always @ (posedge clk)if (!reset) count<=4'b0000; else if (load) count<=d; //这个又少了ifelse if (count==4'b0000) count<=4'b1001; else count<=count-1;

endmodulemodule counter10_tb; wire [3:0] count; reg clk,reset,load; reg [3:0] d; counter10 c10(count, clk, reset,load,d);//这个没有忘always #5 clk = ~clk;initialbeginclk=0;reset=1;load=1;d=4'b1001#5 load=0; #50 reset=0;#50 load=1;d=4'b0000;# 5 load=0; end //又忘了个endendmodule修改测试代码

module counter10_tb; wire [3:0] count; reg clk,reset,load; reg [3:0] d; counter10 c10(count, clk, reset,load,d);always #5 clk = ~clk;initialbeginclk=0;reset=1;load=1;d=4'b1001;#10 load=0; #50 reset=0;#10 reset=1;load=1;d=4'b0000;#10 load=0; end //又忘了个end/*initialbeginclk=0;reset=0;load=0;#10 reset=1;load=1;d=4'b1001;#10load=0;end //又忘了个e

*/

endmodule

最后

总结:

不够细心,

本来应该能答对的

有可能是手跟不上脑子吧

2022-11-30 15:39

这篇博客能写好的原因是:站在巨人的肩膀上

这篇博客要写好的目的是:做别人的肩膀

开源:为爱发电

学习:为我而行